August 2022

## RCL DUAL INTENSITY, SIX CHANNEL LED DRIVER WITH FAULT DETECTION

#### **GENERAL DESCRIPTION**

The IS32LT3181 is a six channels linear current regulator for automotive rear tail light applications such as RCL (Rear Combination Lamps) and CHMSL (Center High Mounted Stop Lamps). It is fully programmable with two LED brightness levels for the different intensity requirements of "stop" bright (DC mode) and "tail" dim (PWM mode).

A logic level at the PWM pin is used to select between the tail and stop output conditions. The stop condition provides the highest intensity output, while the tail condition utilizes an internally generated PWM signal to reduce the intensity of the LEDs' light output.

An active low fault output signal reports a device error condition. The FAULTB pin of several devices can be tied together to disable all the output stages when a fault is detected by any one of the devices.

The sink current at the OUTx pins is easily set with a single resistor at the STOP pin. The constant-current sink outputs can be combined in parallel to create higher current-driving capability on a single string. A second resistor at the TAIL pin sets the duty cycle of the internal PWM oscillator for dimming the LED output when operating in the tail condition.

An external FET (optional) can be implemented for operation with wide varying supply voltages to minimize device thermal dissipation.

The IS32LT3181 is offered in an eTSSOP-16 package.

#### FEATURES

- Operating voltage from 6V to 42VDC

Withstand 50V load dump

- 6 constant-current channel sinks

- Adjustable from 10mA to 75mA per channel

- Channel paralleling for higher current

- Low dropout voltage of 0.8V@35mA

- Slew rate control on each output for better EMI performance

- Integrated PWM dimming engine provides two LED brightness levels without external logic

- Tail duty cycle programmable from 1% to 95%

PWM logic level input selects between full brightness and PWM dimming levels

- Support for optional FET to minimize device power consumption

- Open Drain FAULTB reporting pin - Programmable FAULTB delay time

- Programmable UVLO threshold

- LED open circuit detection

- STOP pin over current protection

- Over temperature protection

- Device disable upon fault detection

Parallel connection to other devices

- AEC-Q100 qualification

- RoHS & Halogen-Free compliant (Pb-free)

package

### APPLICATIONS

- Rear Combinational Lamp (RCL)

- Center High Mount Stop Light (CHMSL)

- Daytime running lamp

- Fog lamps

- Turn signal

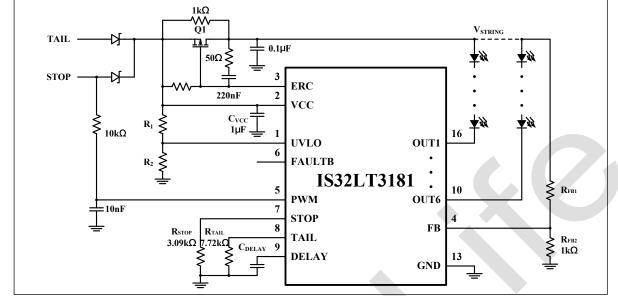

## TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit

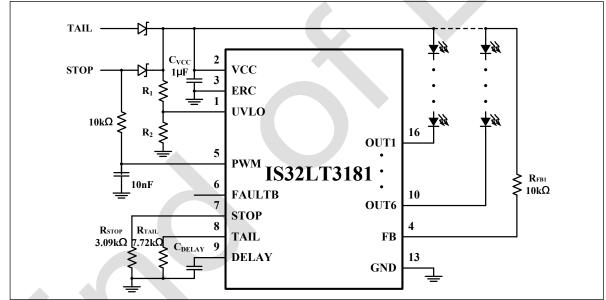

Figure 2 Typical Application Circuit (Without External FET)

## **TYPICAL APPLICATION CIRCUIT (CONTINUE)**

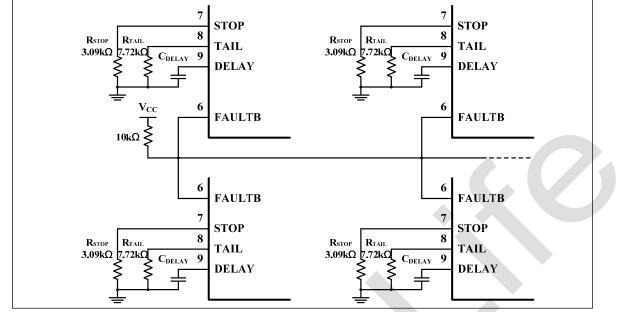

Figure 3 Several Devices Connect FAULTB Pin In Parallel

## **PIN CONFIGURATION**

| Package   | Pin Configuration (Top view)                                                                                                                                                                                                    |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| eTSSOP-16 | UVL0    1     16    OUT1      VCC    2    15    OUT2      ERC    3    14    OUT3      FB    4    13    GND      PWM    5    12    OUT4      FAULTB    6    11    OUT5      STOP    7    10    OUT6      TAIL    8    9    DELAY |  |  |  |  |

## **PIN DESCRIPTION**

| No.   | Pin         | Description                                                                                                                                                                          |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | UVLO        | A resistive voltage divider from VCC to GND sets the under voltage lockout to prevent false triggering during power up.                                                              |

| 2     | VCC         | Power input for the IC.                                                                                                                                                              |

| 3     | ERC         | External regulator control output. Drive the gate of an external PMOS FET to operate it in linear voltage regulator mode.                                                            |

| 4     | FB          | Reference input voltage for the external resistor divider<br>(1.05V typical) for voltage regulation. If no external PMOS<br>FET is used then connect to VCC with a 10k ohm resistor. |

| 5     | PWM         | Digital logic input. Logic high to select full intensity (DC output current) and logic low (or floating) to select lower intensity (PWM output current).                             |

| 6     | FAULTB      | Active low open drain fault flag to indicate error condition.<br>This pin can be connected to other device FAULTB pins to<br>disable LED array under a fault condition.              |

| 7     | STOP        | Resistor to GND on this pin globally sets the maximum sink current for each LED channel.                                                                                             |

| 8     | TAIL        | Resistor to GND on this pin sets the duty cycle of the internally generated PWM signal which determines the lower LED intensity TAIL condition.                                      |

| 9     | DELAY       | Capacitor to GND on this pin sets a delay time before fault<br>reporting. The minimum capacitor value is 10pF. This pin<br>CANNOT be left floating.                                  |

| 10~12 | OUT6 ~OUT4  | Output current sink channel 6~4.                                                                                                                                                     |

| 13    | GND         | Ground connection for the IC.                                                                                                                                                        |

| 14~16 | OUT3 ~ OUT1 | Output current sink channel 3~1.                                                                                                                                                     |

|       | Thermal Pad | Connect to GND.                                                                                                                                                                      |

#### ORDERING INFORMATION Automotive Range: -40°C To +125°C

| Order Part No.                        | Package              | QTY                  |

|---------------------------------------|----------------------|----------------------|

| IS32LT3181-ZLA3-TR<br>IS32LT3181-ZLA3 | eTSSOP-16, Lead-free | 2500/Reel<br>96/Tube |

Copyright © 2022 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

### ABSOLUTE MAXIMUM RATINGS

| -0.3 to 50V    |

|----------------|

| -0.3 to 5.5V   |

| 100mA          |

| 150°C          |

| -55°C ~ +150°C |

| -40°C ~ +150°C |

| 39.9°C/W       |

| 3.1W           |

| ±2kV           |

| ±750V          |

|                |

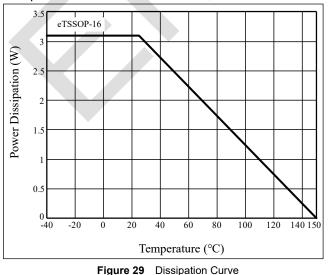

**Note 1:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. **Note 2:** Refer to Figure 29, package power derating curve on Page 15.

**ELECTRICAL CHARACTERISTICS**

Valid are at T<sub>J</sub> = -40°C ~+150°C, V<sub>CC</sub> = 6V~16V, R<sub>STOP</sub> =3.09kΩ, R<sub>TAIL</sub> =7.72kΩ, unless otherwise noted (Note 3)

| Symbol                        | Parameter                    | Condition                                                                                                                          | Min. | Тур. | Max. | Unit  |  |

|-------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Vcc                           | Supply voltage               |                                                                                                                                    | 6    |      | 42   | V     |  |

| lcc                           | Input current                | l <sub>OUTx</sub> =35mA, V <sub>CC</sub> =16V, 6 channels<br>T <sub>J</sub> = -40°C ~+125°C                                        |      | 6.0  | 8.0  | mA    |  |

|                               |                              | T <sub>J</sub> = +150°C (Note 5) 6.0                                                                                               |      |      |      |       |  |

| IOUT_MAX                      | Maximum sink current         | V <sub>OUTx</sub> =1.2V                                                                                                            | 75   |      |      | mA    |  |

| IOUTACC Sink current accuracy |                              | Ioutx = 35mA = (Iout_MAX+Iout_MIN)/2<br>Voutx = 0.8V, TJ = -40°C ~+125°C<br>(Note 4)                                               | -10  | 0    | 10   | %     |  |

|                               |                              | T <sub>J</sub> = +150°C                                                                                                            | -12  | 0    | 12   |       |  |

| ΔΙουτ C                       | Current matching             | 1-2×Іоцт/(Іоцт_мах+Іоцт_мім)<br>Іоцтх =35mA, Тј = -40°С ~+125°С                                                                    | -5   | 0    | 5    | %     |  |

|                               |                              | T <sub>J</sub> = +150°C                                                                                                            | -7   | 0    | 7    |       |  |

| ١L                            | Current leakage              | V <sub>OUTx</sub> =42V                                                                                                             |      |      | 1    | μA    |  |

| L <sub>R</sub>                | Line regulation              | 6V< V <sub>CC</sub> <16V, 0.8V <v<sub>OUTx&lt;3V<br/>I<sub>OUTx</sub> = 35mA, 6 channels<br/>T<sub>J</sub> = -40°C ~+125°C</v<sub> |      | 0.6  | 4    | mA    |  |

| Voc                           | Open LED detection threshold |                                                                                                                                    | 0.3  | 0.45 | 0.6  | V     |  |

| Vтн                           | Output disable threshold     |                                                                                                                                    |      | 100  | 250  | mV    |  |

| Rcs                           | Current slew rate            | l <sub>OUTx</sub> = 35mA, 10%~90%<br>Τ <sub>J</sub> = -40°C ~+125°C                                                                |      | 5    | 20   | mA/µs |  |

|                               |                              | T <sub>J</sub> = +150°C (Note 5)                                                                                                   |      | 5    |      |       |  |

### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Valid are at  $T_J = -40^{\circ}C \sim +150^{\circ}C$ ,  $V_{CC} = 6V \sim 16V$ ,  $R_{STOP} = 3.09k\Omega$ ,  $R_{TAIL} = 7.72k\Omega$ , unless otherwise noted (Note 3)

| Symbol                        | Parameter                                           | Condition                                                                                | Min. | Тур. | Max. | Unit |

|-------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| T <sub>SD</sub>               | Thermal shutdown Threshold                          | (Note 5)                                                                                 | 150  | 160  |      | °C   |

| TSD_HY                        | Thermal hysteresis                                  | (Note 5)                                                                                 |      | 15   |      | °C   |

| VFAULTB                       | FAULTB pin voltage                                  | Sink current = 5mA                                                                       |      | 0.1  | 0.2  | V    |

| VFAULT_H                      | FAULTB pin high enable threshold                    | Voltage rising                                                                           |      |      | 2    | V    |

| V <sub>FAULT_L</sub>          | FAULTB pin low disable threshold                    | Voltage falling                                                                          | 0.6  |      |      | v    |

| Vuvlo_th                      | FAULTB reporting under voltage locked out threshold | Voltage rising                                                                           | 1.1  | 1.2  | 1.35 | V    |

| $V_{\text{UVLO}_{\text{HY}}}$ | Hysteresis of UVLO                                  |                                                                                          |      | 100  |      | mV   |

| VDELAY                        | DELAY pin voltage threshold                         |                                                                                          | 1.1  | 1.2  | 1.35 | V    |

| IDELAY                        | DELAY pin source current                            |                                                                                          | 1.5  | 2    | 2.5  | μA   |

| ILF                           | FAULTB pin input leakage current                    | VFAULTB = 20V                                                                            |      | 0.1  | 1    | μA   |

| V <sub>PWM_H</sub>            | PWM high threshold                                  |                                                                                          |      | 1.9  | 2.2  | V    |

| Vpwm_l                        | PWM minimum threshold                               |                                                                                          | 0.7  | 1.0  |      | V    |

| Vfb                           | FB regulation voltage                               |                                                                                          | 0.95 | 1.05 | 1.15 | V    |

| I <sub>ERC</sub>              | ERC drive current                                   | V <sub>ERC</sub> ≥3V                                                                     | 5    | 6    |      | mA   |

| VSTOP                         | STOP pin output voltage                             | T <sub>J</sub> = -40°C ~+125°C (Note 4)                                                  | 1.05 | 1.08 | 1.11 | V    |

|                               | STOP pin current to IOUTX                           | (Note 4)                                                                                 |      | 100  |      | A/A  |

| Itail                         | TAIL pin output current                             |                                                                                          | 90   | 100  | 110  | μA   |

|                               |                                                     | Duty cycle set to 5%, V <sub>TAIL</sub> = 0.6V                                           | 2.5  | 5    | 7.5  | %    |

|                               | PWM accuracy                                        | Duty cycle set to 50%, V <sub>TAIL</sub> = 2.4V                                          | 45   | 50   | 55   | %    |

|                               |                                                     | Duty cycle set to 80%, V <sub>TAIL</sub> = 3.6V                                          | 70   | 80   | 90   | %    |

| ton                           | Turn-on delay                                       | $V_{CC}$ =0V step to $V_{CC}$ =12V, the delay between 0.9× $V_{CC}$ with 0.9× $I_{OUTx}$ |      | 1    | 2    | ms   |

| tрwм                          | PWM on delay                                        | V <sub>CC</sub> =12V V <sub>PWM</sub> =12V step to V <sub>PWM</sub><br>=0V               |      | 50   | 100  | μs   |

| fewm                          | PWM frequency                                       | V <sub>PWM</sub> = 0V                                                                    |      | 1    |      | kHz  |

**Note 3:** All parts are production tested at  $T_J = -40^{\circ}C \sim +150^{\circ}C$ , unless otherwise noted. Other temperature limits are guaranteed by design. **Note 4:** Accuracy of the STOP pin output voltage need not meet the specification so long as the output current accuracy specification over the full programmable current range can be guaranteed.

Note 5: Guaranteed by design.

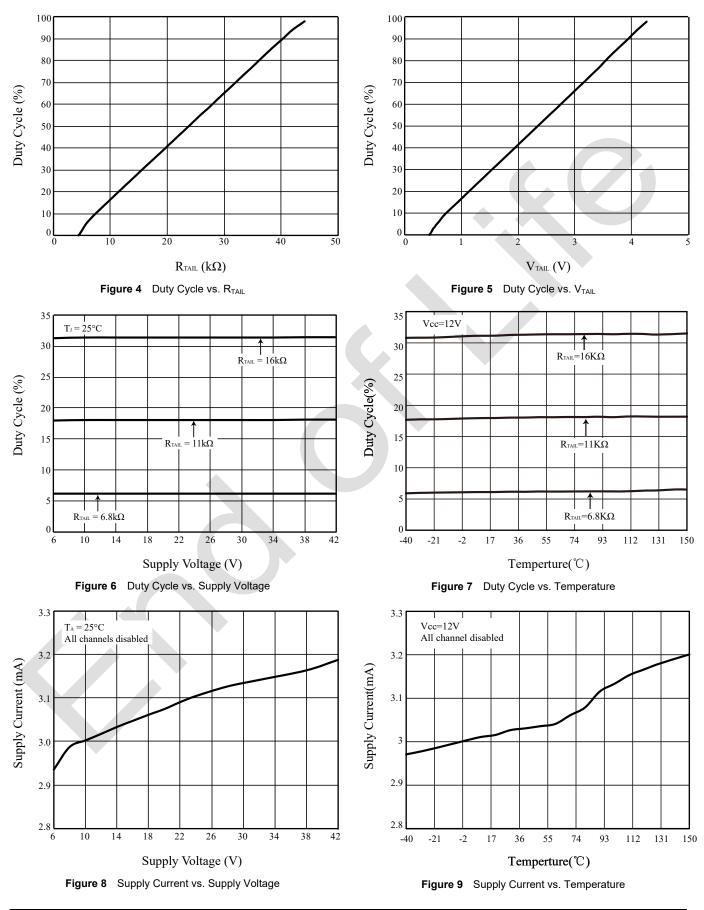

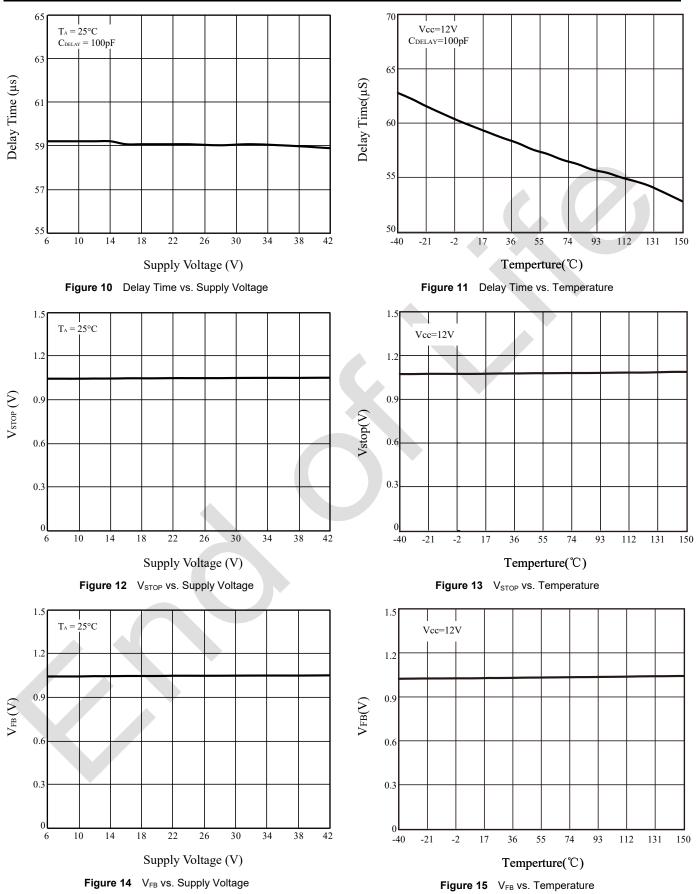

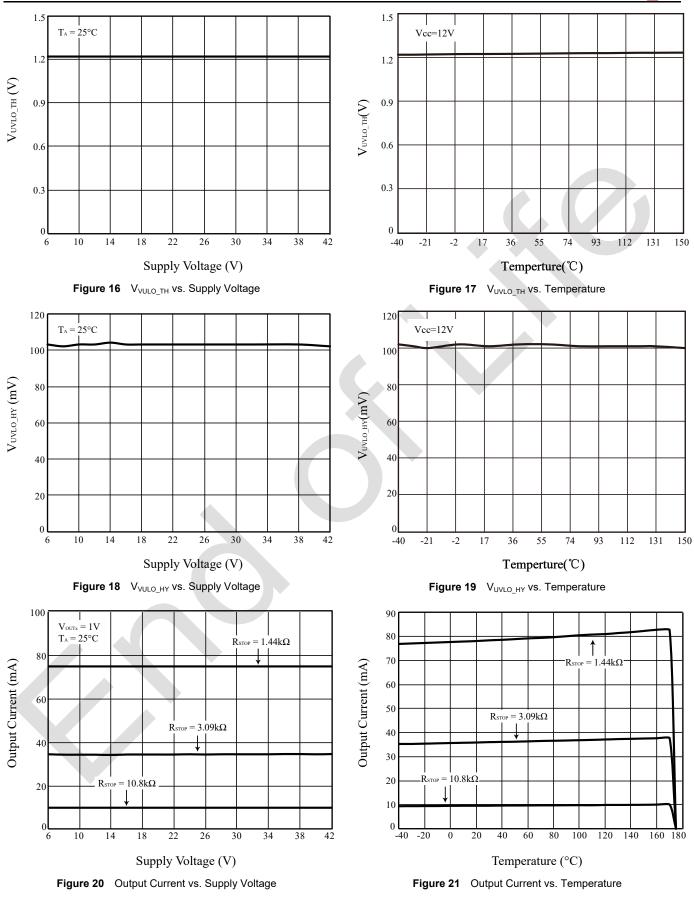

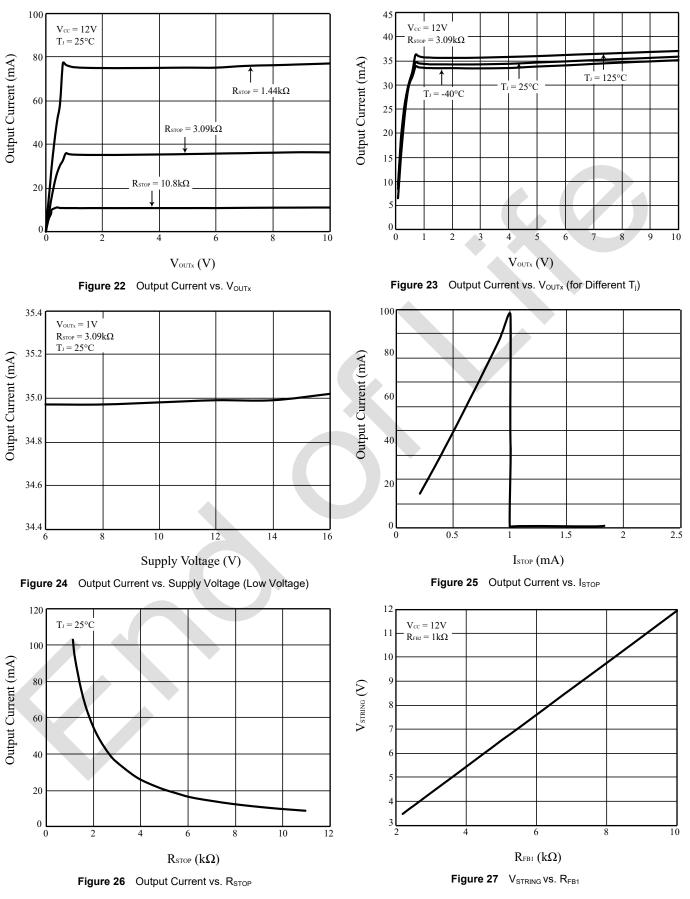

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Lumissil Microsystems – www.lumissil.com Rev. D, 08/26/2022

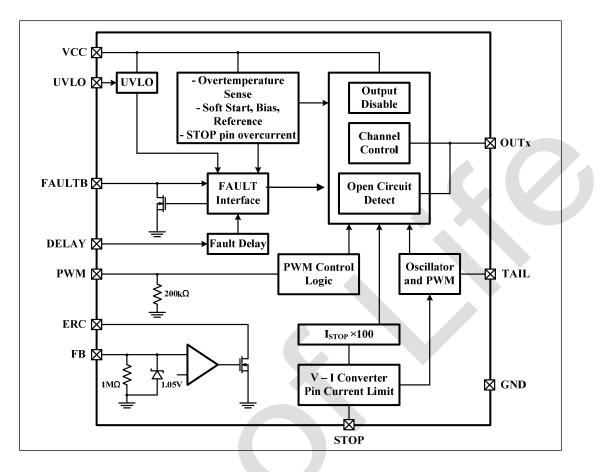

## FUNCTIONAL BLOCK DIAGRAM

#### APPLICATION INFORMATION

The IS32LT3181 is a 6-channel linear current driver optimized to drive Rear Combination Lamp for automotive applications. A single input is used to select between two fully programmable intensity levels, one for the 'STOP' condition, and the other for the 'TAIL' condition. The full intensity 'STOP' condition is easily set using an external resistor, R<sub>STOP</sub>. The lower intensity 'TAIL' condition is realized via an integrated PWM circuit, the duty cycle of which is easily programmed using an external resistor, R<sub>TAIL</sub>.

IS32LT3181 also includes an integrated drive circuit for an external PMOS FET linear regulator for the case where the voltage across the LED loads must be accurately maintained to control power dissipation.

The ERC pin current ( $I_{ERC}$ ) flows through 1k $\Omega$  resistor ( $R_{GS}$ ) and generates a voltage across gate and drain of PMOS FET. IS32LT3181 regulates this ERC current by sensing feedback reference voltage (V<sub>FB</sub>) to control the R<sub>DS\_ON</sub> of PMOS FET and get the expected V<sub>STRING</sub>, which is set by resistor divider R<sub>FB1</sub> and R<sub>FB2</sub>.

The integrated feedback reference is trimmed to be 9% accuracy, while the ERC pin current ( $I_{ERC}$ ) for the external regulator control can drive up to 6mA.

#### PROGRAMMING THE OUTPUT CURRENT

A single programming resistor ( $R_{STOP}$ ) controls the maximum sink current for each LED channel. The STOP pin provides a reference voltage of 1.08V (Typ.). The programming resistor may be computed using the following Equation (1):

$$I_{OUT} = 100 \times \frac{1.08V}{R_{STOP}} \tag{1}$$

The current which is drawn from the STOP pin is internally mirrored to each of the 6 outputs with a multiplication factor of 100A/A. Thus, an output current of 50mA would require a current to be drawn from STOP of 500 $\mu$ A, corresponding to an external programming resistance of 2.16k $\Omega$ .

#### **OVER CURRENT PROTECTION**

A 1mA current limiting on STOP pin limits the current which can be referenced from the STOP pin. Exceeding the STOP pin current limit will shut down the output currents to prevent unexpected excessive power dissipation (Figure 10). When the STOP pin current reaches 1mA, the current outputs are shutdown, the fault register is triggered and FAULTB pin will be asserted low after the FAULTB delay time.

#### PROGRAMMING THE PWM DUTY CYCLE

A single external resistor on the TAIL pin sets the PWM duty cycle which determines the lower intensity TAIL condition. The TAIL pin supplies a constant

current of 100 $\mu$ A. The PWM duty cycle (D<sub>cycle</sub>) is set by the following Equation (2):

$$D_{cycle} = \left(\frac{100\mu A \times R_{TAIL}}{4V} - 0.1\right) \times 100\%$$

(2)

Internally, a sawtooth waveform with a peak value of 4.4V and a minimum value of 0.4V is compared to the voltage of the TAIL pin (100uA x R<sub>TAIL</sub>). The fixed frequency of the sawtooth waveform is 1kHz resulting in a PWM signal of 1kHz at the programmed duty cycle. Thus, for example, a 50% duty cycle would require the reference voltage at TAIL to be 2.4V, corresponding to an external resistance value of 24k $\Omega$ .

The internal PWM generator can also be driven by an external DC voltage supply. Providing a DC input voltage to the TAIL pin in the range from 0.4V to 4.4V programs the output duty cycle linearly from 0% to 100% duty cycle.

#### THERMAL SHUTDOWN

If the die temperature exceeds the thermal shutdown temperature of 160°C (Typ.) then the device will shutdown, and the sink currents are shut off for all channels. After a thermal shutdown event, the IS32LT3181 will not try to restart until its temperature has reduced to less than 145°C (Typ.). The fault register is triggered and FAULTB pin will be asserted low after delay time.

#### OUTPUT CURRENT SLEW RATE CONTROL

To minimize the effects of EMI, the output current rise and fall time is controlled. The slew rate control circuitry is designed to control the rise time, 10% to 90% and fall time 90% to 10% at  $5mA/\mu s$  (Typ.).

#### **OPEN LED DETECTION**

Each of the outputs of the IS32LT3181 is monitored for an output voltage of less than 450mV (Typ.). If any of the output voltages drops below the threshold voltage, the fault register is triggered and the FAULTB pin is asserted low after delay time.

During normal operation, it is possible that current may still be flowing in the output LED string even if the output voltage of the IC falls below the OC detect threshold – for example, if the LED string remains intact, but the supply voltage dips momentarily (the duration is longer than  $t_D$  which is configured by the DELAY pin) and UVLO pin remain higher than threshold. In this case, the FAULTB pin would assert then de-assert when the output voltage returns to the nominal value.

#### **OUTPUT DISABLE DETECTION**

As IS32LT3181 powers up, the device will check OUTx pin of each channel to see if it is connected to GND. If any channel is connected to GND (disable typical threshold is 100mV), the fault diagnostic function will ignore the fault of this channel. To prevent a trigger fault assertion, when less than 6 channels are used, the unused OUTx pins must be connected to GND to disable these channels.

| 6V< V <sub>CC</sub> <16V (V <sub>UVLO</sub> >1.2V) |               |                                                     |             |  |  |  |

|----------------------------------------------------|---------------|-----------------------------------------------------|-------------|--|--|--|

| PWM<br>Pin                                         | LED<br>String | Ιουτ                                                | FAULTB      |  |  |  |

| > 2.2V                                             | Normal        | $100 \times \frac{1.08}{R_{STOP}}$                  | De-asserted |  |  |  |

|                                                    | Open          | 0A                                                  | Asserted    |  |  |  |

| <0.7V                                              | Normal        | $100 \times \frac{1.08}{R_{STOP}} \times D_{cycle}$ | De-asserted |  |  |  |

|                                                    | Open          | 0A                                                  | Asserted    |  |  |  |

#### Table 1 IOUT and FAULTB State at Different PWM

D<sub>cycle</sub> = Duty cycle of PWM as set by R<sub>TAIL</sub>.

#### EXTERNAL REGULATOR CONTROL PIN

An external PMOS can be used to protect the IS32LT3181 and the LED strings from damage due to large voltage variation on the supply input voltage. The external PMOS is used as a linear voltage regulator to help minimize the power dissipated in the IS32LT3181 device.

Two modes of operation can be selected by external connection of the FB pin as described below.

1) The first mode of operation is selected by connecting the FB pin to VCC through a  $10k\Omega$  (as shown in the Figure 2 typical operating schematic). In this mode, the linear voltage regulator is disabled and the total LED V<sub>F</sub> should be close to the supply voltage (V<sub>CC</sub> - V<sub>OUTx</sub>) for minimal IS32LT3181 package thermal dissipation.

2) The second mode of operation is selected by connecting a resistive voltage divider to the FB pin (as shown in the Figure 1 typical operating schematic). This enables the ERC pin output to linearly drive the PMOS FET and regulate the V<sub>STRING</sub> voltage so the FB voltage is maintained at 1.05V (Typ.).

#### FEEDBACK VOLTAGE SETTING

V<sub>STRING</sub> should be set to a level to allow proper operation of the IC without detecting an open LED (0.6V max on OUTx) and to keep power to the IC at reduced levels below the 160°C (Typ.) thermal shutdown threshold limit. Reducing die temperature will depend on printed circuit board composition, PCB size, thermal via number and placement, module component placement, and air flow.

$V_{\text{STRING}}$  can only be adjusted with an external PMOS FET and it is set using resistors  $R_{FB1}$  and  $R_{FB2}$  (refer to Figure 1) as following Equation (3):

$$V_{STRING} = V_{FB} \times \left(\frac{R_{FB1}}{R_{FB2}} + 1\right)$$

(3)

LUMISSIL

A Division of

This simplifies to an Equation (4) for R<sub>FB1</sub>.

$$R_{FB1} = \frac{R_{FB2} \left( V_{STRING} - V_{FB} \right)}{V_{FB}} \tag{4}$$

Where  $V_{FB} = 1.05V$  (Typ.)

And,

$$V_{STRING} = V_{OUTx} + V_{LED}$$

(5)

The recommended R<sub>FB2</sub> is  $1k\Omega$ . V<sub>LED</sub> is the total LED string forward voltage drop, V<sub>F</sub>. V<sub>OUTx</sub> should be selected for optimal current sink operation. Please refer to Figure 22 and 23 to set a proper V<sub>OUTx</sub>.

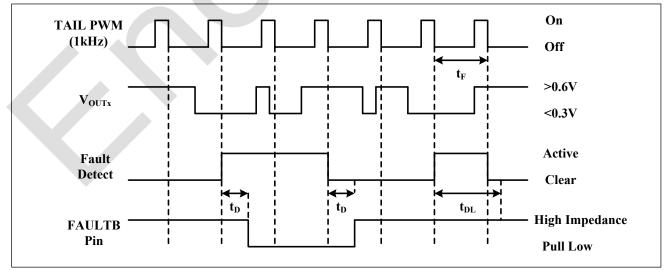

### FAULTB OUTPUT OPERATION

The FAULTB pin is an open drain structure. When a fault is asserted, the pin will change from high impedance to pull low state. If it is externally connected to a pull-up resistor, it will be at the pull-up voltage after fault is released. The FAULTB pin is also an input pin. When the voltage of this pin is pulled up to exceed  $V_{FAULT_H}$ , all the outputs will be enabled. To shutdown the output, the FAULTB pin voltage has to drop lower than  $V_{FAULT_L}$ . Several devices with their FAULTB pins connected in parallel act to turn off all the interconnected devices. Any device which encounters a fault will turn off all the other devices. Please refer to Figure 3 schematic.

A FAULTB pin assertion can be delayed. This fault delay time consists of T1 and T2. T1 is the built-in deglitch time. If an open LED fault occurs, T1 is about 4 $\mu$ s. If R<sub>STOP</sub> pin over current fault or thermal shutdown occurs, T1 is about 100ns. T2 can be set by connecting a capacitor from the DELAY pin to GND. The device internally sources a 2 $\mu$ A (I<sub>DELAY</sub>) current to charge this capacitor and monitor the voltage of this pin. Once it reaches the threshold voltage of 1.2V (V<sub>DELAY</sub>), the FAULTB pin will be asserted. So the delay time t<sub>D</sub> can be calculated by the following Equation (6):

$$t_D = \frac{V_{DELAY} \times C_{DELAY}}{I_{DELAY}}$$

(6)

Note: The minimum value of this delay capacitor  $C_{\text{DELAY}}$  is 10pF. The DELAY pin CANNOT be left floating.

In all fault cases, if the device is powered down during the time when the FAULTB signal is asserted, the FAULTB pin is reset. Reapplying power to the circuit after this has occurred will cause the FAULTB pin to operate as normal in accordance with the conditions described below.

The LED(s) open fault reporting is enabled by UVLO pin voltage exceeding the UVLO threshold. A resistive voltage divider from VCC to GND is used for

preventing false triggering during power up. The fault UVLO voltage could be set by the following equation (7):

$$V_{UVLO} = V_{UVLO_{TH}} \times \left(\frac{R_1}{R_2} + 1\right)$$

(7)

To disable the FAULTB reporting, the UVLO pin voltage has to drop more 100mV lower than  $V_{\text{UVLO}_{TH}}$ .

When the voltage of UVLO pin exceeds  $V_{UVLO_TH}$ , any channel which encounters an open LED condition (the voltage of the OUTx pin falls lower than 0.6V) will remain on state, turn off all the other channels and be asserted by the FAULTB pin after delay time. Typically this condition is encountered during a STOP or TAIL

condition then the fault condition will be detected and the fault signal asserted after delay time. When the IS32LT3181 is in neither STOP nor TAIL condition, the circuit is powered down, and the signal is cleared. Upon re-entering either the STOP or TAIL condition, the fault signal will reassert after delay time and the output will remain off, if the fault condition still exists. If the fault condition has been cleared, FAULTB pin will not re-assert and all the other channels will be turned on.

Exceeding the STOP pin current limiting 1mA will turn off all the channels and the FAULTB pin will assert after delay time (refer to Figure 28). This fault assertion will be reset after fault condition cleared.

| Table 2 Fault Assertion             |                                                     |                                                                             |                      |                                                                                                                             |                                                 |  |

|-------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| Fault Type                          | Test Condition                                      | Output Driver<br>Action                                                     | FAULTB Pin<br>Output | Fault Logic Decision                                                                                                        | Fault<br>Recovering                             |  |

|                                     | Vout<0.45V,<br>Vuvlo> 1.2V                          | Keeping the<br>open channel<br>on and turning<br>the other<br>channels off. | Pulled Low           | For stop mode, Fault state<br>will be reported after fault<br>delay time t <sub>D</sub> .                                   | V                                               |  |

| LEDs Open<br>(1 to 6 LED<br>string) |                                                     |                                                                             |                      | For Tail mode, Fault state<br>can be reported due to fault<br>delay time t <sub>D</sub> and PWM<br>signal. ( See Figure 28) | Vouτ exceeds<br>0.45V.                          |  |

|                                     | V <sub>OUT</sub> <0.45V,<br>V <sub>UVLO</sub> <1.2V | All channels<br>turn on                                                     | High impedance       | NA                                                                                                                          | NA                                              |  |

| RSTOP PIN<br>Over Current           | Irstop>1mA                                          | All channels<br>shutdown                                                    | Pulled Low           | Fault state will be reported after fault delay time t⊳.                                                                     | I <sub>RSTOP</sub> falls lower<br>than 1mA.     |  |

| Thermal<br>shutdown                 | Tյ>160°C                                            | All channels<br>shutdown                                                    | Pulled Low           | Fault state will be reported after fault delay time t <sub>D</sub> .                                                        | The junction<br>temp falls lower<br>than 145°C. |  |

Figure 28 Fault detect during TAIL mode

Note 1: In TAIL mode, the fault detection is implemented only at the PWM falling edge.

Note 2:  $t_{DL}$  means a long fault delay time.  $t_F$  means the fault detect state change time. If  $t_{DL}$  is longer than  $t_F$ , the FAULTB pin will not report the fault.

#### THERMAL DISSIPATION

The package thermal resistance,  $\theta_{JA}$ , determines the amount of heat that can pass from the silicon die to the surrounding ambient environment. The  $\theta_{JA}$  is a measure of the temperature rise created by power dissipation and is usually measured in degree Celsius per watt (°C/W). The junction temperature, T<sub>J</sub>, can be calculated by the rise of the silicon temperature,  $\Delta T$ , the power dissipation on IS32LT3181, P<sub>3181</sub>, and the package thermal resistance,  $\theta_{JA}$ , as in Equation (8):

$$P_{3181} = V_{CC} \times I_{CC} + \sum_{x=1}^{6} V_{OUTx} \times I_{OUTx}$$

(8)

and,

So,

$$T_J = T_A + \Delta T = T_A + P_{3181} \times \boldsymbol{\theta}_{JA}$$

(9)

Where, V<sub>CC</sub> is the supply voltage, V<sub>OUTx</sub> is the voltage across OUTx pin to GND,  $I_{OUTx}$  is the sink current of each LED string and T<sub>A</sub> is the ambient temperature.

When operating the device at high ambient temperatures, or when driving high load current, care must be taken to avoid exceeding the package power dissipation limits. The maximum power dissipation can be calculated using the following Equation (10):

$$P_{D(MAX)} = \frac{150^{\circ}C - 25^{\circ}C}{\theta_{JA}}$$

(10)

$$P_{D(MAX)} = \frac{150^{\circ}C - 25^{\circ}C}{39.9^{\circ}C/W} \approx 3.1W$$

Figure 29, shows the power derating of the IS32LT3181 on a JEDEC board (in accordance with JESD 51-5 and JESD 51-7) standing in still air.

When the junction temperature, T<sub>J</sub>, exceeds the absolute maximum temperature 150°C (Typ.), the optional external linear voltage regulator configuration should be implemented in order to withstand unwanted dissipation.

Lumissil Microsystems – www.lumissil.com **Rev. D, 08/26/2022**

With the linear voltage regulator, IS32LT3181 will regulate the PMOS FET to keep  $V_{\text{STRING}}$  voltage constant, that can be set by resistor divider  $R_{\text{FB1}}$  and  $R_{\text{FB2}}$ . So even though the supply voltage  $V_{\text{CC}}$  has some variation, the power dissipation on IS32LT3181 will be constant.

$$V_{OUTx} = V_{STRING} - V_{LEDSx}$$

(11)

And,

$$P_{3181} = V_{CC} \times I_{CC} + \sum_{x=1}^{6} V_{OUTx} \times I_{OUTx}$$

(12)

Where,  $V_{\text{LEDSx}}$  is the total forward voltage of each LED string.

The power dissipation on the external PFET MOS can be calculated by the following Equation (13):

$$P_{FET} = \sum_{x=1}^{6} (V_{CC} - V_{STRING}) \times I_{OUTx}$$

(13)

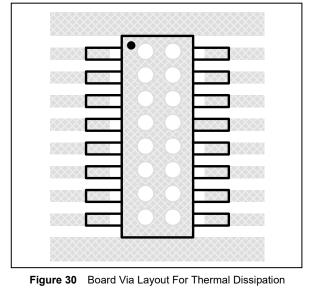

When designing the Printed Circuit Board (PCB) layout, double-sided PCB with a copper area of a few square millimeters on each side of the board directly under the IS32LT3181 (eTSSOP-16 package) and PMOS FET must be used. Multiple thermal vias will help to conduct heat from the exposed pad of the IS32LT3181 and PMOS FET to the copper on each side of the board. The thermal resistance can be further reduced by using a metal substrate or by adding a heat sink.

The thermal resistance is achieved by mounting the IS32LT3181 on a standard FR4 double-sided printed circuit board (PCB) with a copper area of a few square inches on each side of the board under the IS32LT3181. Multiple thermal vias, as shown in Figure 30, help to conduct the heat from the exposed pad of the IS32LT3181 to the copper on each side of the board. The thermal resistance can be reduced by using a metal substrate or by adding a heatsink.

•

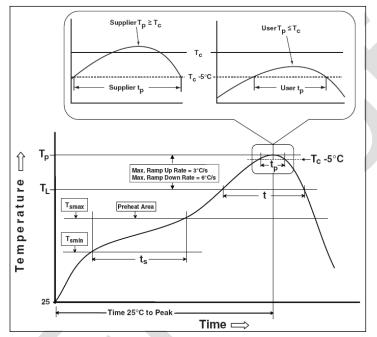

### **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                                    | Pb-Free Assembly                 |

|----------------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak<br>Temperature min (Tsmin)<br>Temperature max (Tsmax)<br>Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                                 | 3°C/second max.                  |

| Liquidous temperature (TL)<br>Time at liquidous (tL)                                               | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                                | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                            | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                               | 6°C/second max.                  |

| Time 25°C to peak temperature                                                                      | 8 minutes max.                   |

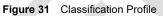

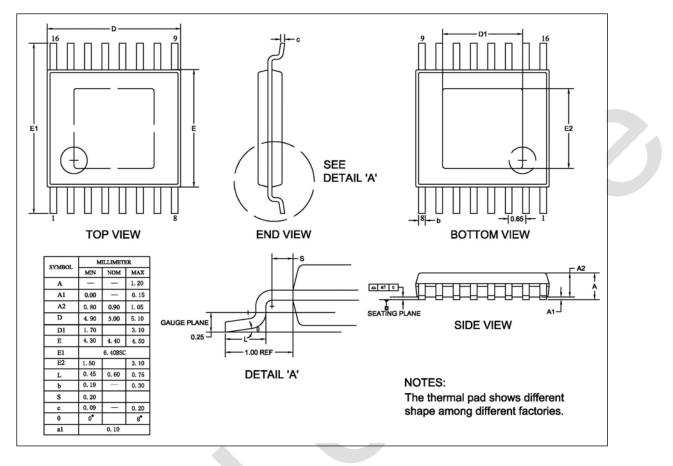

### PACKAGE INFORMATION

#### eTSSOP-16

## RECOMMENDED LAND PATTERN

#### Note:

1. Land pattern complies to IPC-7351.

2. All dimensions in MM.

3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. user's board manufacturing specs), user must determine suitability for use.

# LUMISSIL MICROSYSTEMS

# IS32LT3181

## **REVISION HISTORY**

| Revision | Detail Information                                                                                                                                 |            |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 0A       | Initial release                                                                                                                                    | 2016.03.11 |

| 0B       | 1. Update EC table<br>2. Update the temperature range of figure 7, 9, 11, 13, 15, 17, 19 to 150°C                                                  | 2016.09.02 |

| А        | AEC-Q100 qualification released.                                                                                                                   | 2016.11.17 |

| В        | Correct I <sub>OUTACC</sub> condition error in EC table: $T_J = -40^{\circ}C \sim +150^{\circ}C$ change to $T_J = -40^{\circ}C \sim +125^{\circ}C$ | 2017.04.20 |

| С        | Add NRND watermark                                                                                                                                 | 2022.06.14 |

| D        | Change watermark to EOL                                                                                                                            | 2022.08.26 |