May 2024

### 12 CHANNELS, LINEAR LED DRIVER WITH UART INTERFACE

#### 1 GENERAL DESCRIPTION

The IS32LT3137 is a linear programmable current regulator consisting of 12 output channels capable of up to 100mA each. It has a UART interface compatible with CANFD PHY for communication with a master microcontroller or ECU. It uses a command and response protocol mastered by the host microcontroller to read and write the registers to and from one or multiple IS32LT3137 devices.

Each output can individually support 12-bit PWM dimming and 7-bit DC current adjustment. The outputs can be combined to provide higher current drive capability to max 1.2A.

For added system reliability, the IS32LT3137 integrates fault detection circuitry for open/short string, single LED short, and over temperature conditions. Faults are recorded in registers which can be accessed by an external MCU. To optimize EMI performance, the IS32LT3137 features spread spectrum on the internal PWM and LED channel outputs have programmable slew rate control and phase delay to mitigate EMI and power supply inrush current.

The IS32LT3137 is targeted at the automotive market such as interior accent lighting and exterior tail lighting. It is offered in WFQFN-32 (5mm×5mm) package.

### 2 APPLICATIONS

- Animation Rear Light

- Animation Tail Light

- Animation Daytime Running Light

#### 3 FEATURES

- Wide input voltage supply from 4.5V to 16V

- Maximum output voltage 16V

- UART Communication Interface

- UART interface compatible with CANFD physical layer, 1MHz maximum.

- UART communication with CRC to ensure robustness of communication

- Support up to max. 16 addressable devices

- Watch dog timer

- Support Fail safe mode

- 12 channels capable of 100mA each

- ±4.5% @ 100mA bit-to-bit output current mismatch

- ±5% @ 100mA device-to-device output current accuracy

- Combined for higher current capability with same current accuracy

- Minimum headroom voltage of 0.5V (Max.) at 100mA

- Individual PWM dimming to each channel

- 4096 steps (12-bit) PWM duty cycle setting

- 7+5-bit at 24kHz

- 12-bit at 244Hz

- 8-bit at 24kHz

- Phase delay minimizes inrush current (4 groups)

- Slew rate control and spread spectrum optimize EMI performance

- 64 steps (6-bit) global current setting

- Individual 128 steps (7-bit) DC current adjustment to each channel

- DC Binning support (ADJR pin)

- Fault protection with reporting

- Fail safe modes selection

- LED string open/short detect

- Single LED short detect

- Programmable fault reporting delay time

- Programmable over temperature current roll off

- Thermal shutdown

- CRC error detection

- ISET short to GND

- AEC-Q100 Qualified with Temperature Grade 1: -40°C to 125°C

- Operating temperature range (-40°C ~ +125°C)

- WFQFN-32 (5mm×5mm) package

- RoHS & Halogen-Free Compliance

- TSCA Compliance

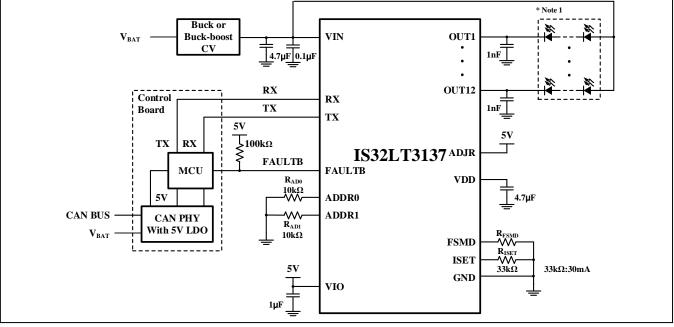

### 4 TYPICAL APPLICATION CIRCUIT

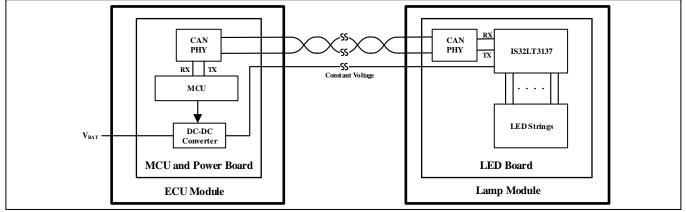

Figure 1 Typical Application Circuit of IS32LT3137 with UART Interface

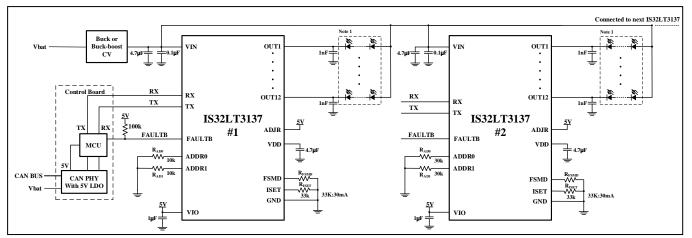

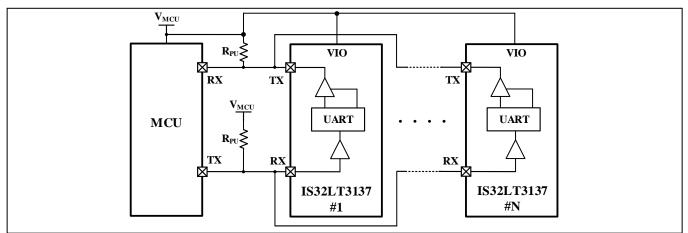

Figure 2 Typical Application Circuit of Multiple IS32LT3137 with UART Interface

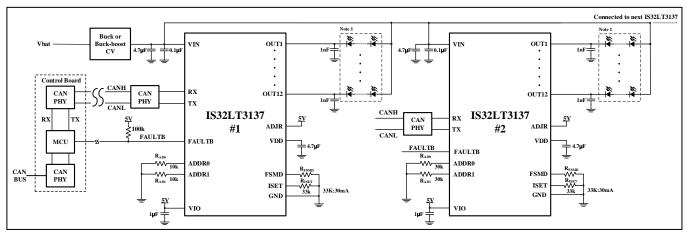

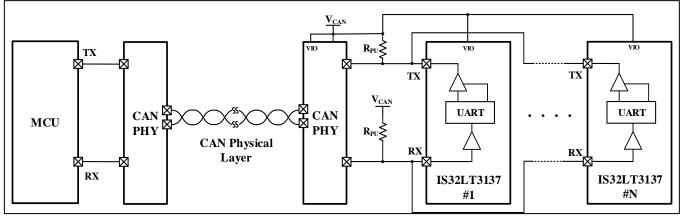

Figure 3 Typical Application Circuit of Multiple IS32LT3137 with External CAN Transceiver for Off-board Long Distance Communication

Note 1: The forward voltage variation of output channels (OUTx) should be kept as smaller as possible to minimize the heat consumption on device and prevent false fault triggering.

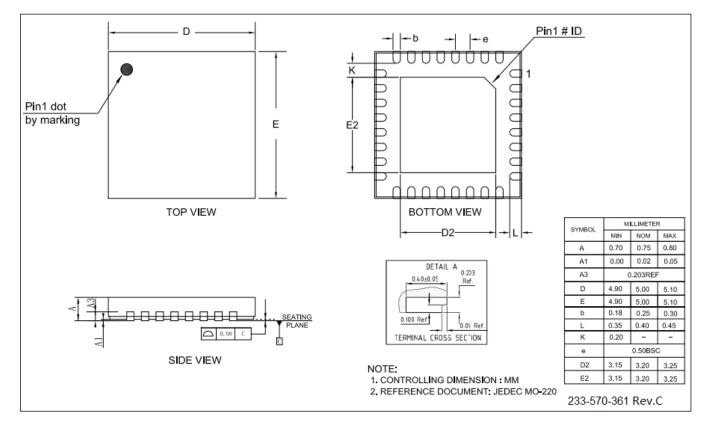

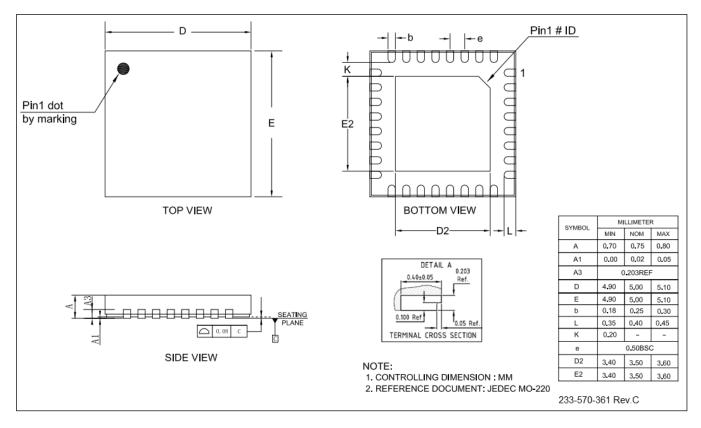

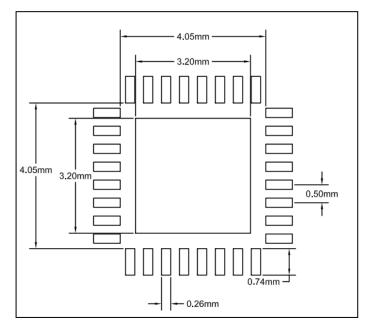

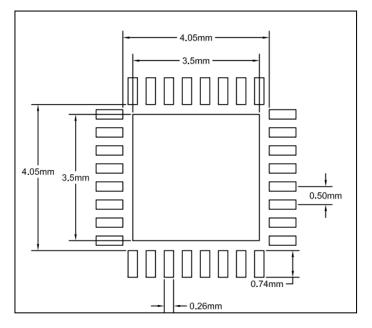

### 5 PIN CONFIGURATION

| Package  | Pin Configuration (Top View)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WFQFN-32 | $\begin{array}{c} \text{VIN} \\ \text{OUT1} \\ \text{OUT1} \\ \text{OUT2} \\ \text{OUT2} \\ \text{OUT3} \\ \text{OUT3} \\ \text{OUT4} \\ \text{OUT5} \\ \text{OUT5} \\ \text{OUT5} \\ \text{OUT6} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT6} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT6} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT6} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT6} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT7} \\ \text{WIN} \\ \text{OUT6} \\ \text{OUT7} \\ \text{WIN} \\ \text{WIN} \\ \text{WIN} \\ \text{UV110} \\ \text{WIN} \\ \text{WIN} \\ \text{WIN} \\ \text{WIN} \\ \text{WIN} \\ \text{UV111} \\ \text{UV110} \\ \text{WIN} \\ \text{UV111} \\ \text{UV111} \\ \text{WIN} \\ \text{UV110} \\ \text{WIN} \\ WIN$ |

### DESCRIPTION

| No.            | Pin         | Description                                                                                                  |

|----------------|-------------|--------------------------------------------------------------------------------------------------------------|

| 1              | VIN         | Power supply input.                                                                                          |

| 2~10,<br>17~19 | OUT1~OUT12  | Current sink channels.                                                                                       |

| 11             | FAULTB      | Open drain fault reporting pin. FAULTB pin is open drain output and requires an external pull-up resistor.   |

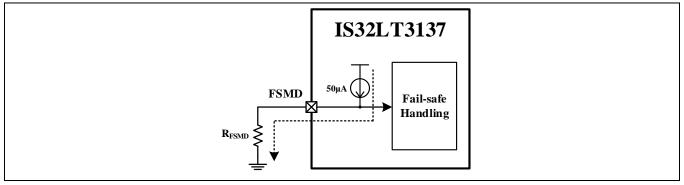

| 12             | FSMD        | Connect resistor to GND to select fail safe mode.                                                            |

| 13             | VIO         | For TX power supply                                                                                          |

| 14             | ТХ          | UART interface transmitted data pin.                                                                         |

| 15             | RX          | UART interface received data pin.                                                                            |

| 16, 31         | GND         | Ground.                                                                                                      |

| 20~25, 30      | NC          | No connection. Pin 30 should be left floating, do not connect to GND or any other pins or signals.           |

| 26             | ISET        | Input pin used to connect an external resistor to set the global output current.                             |

| 27             | ADJR        | For analog dimming control                                                                                   |

| 28~29          | ADDR0~ADDR1 | Address setting. Connect different values resistors from these pins to GND to assign device address.         |

| 32             | VDD         | 4.2V LDO output. Connect a 4.7µF X7R capacitor to GND.                                                       |

|                | Thermal Pad | Must be connected to GND. Connect thermal pad to external GND plane on board for better thermal performance. |

#### 6 ORDERING INFORMATION Automotive Range: -40°C to +125°C

| Order Part No.                                       | Package             | QTY/Reel |

|------------------------------------------------------|---------------------|----------|

| IS32LT3137-QWLA3-TR<br>IS32LT3137-QWLCA3-TR (Note 2) | WFQFN-32, Lead-free | 2500     |

Note 2: IS32LT3137-QWLCA3-TR is with copper wire bonding.

Copyright © 2024 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

### 7 SPECIFICATIONS

### 7.1 ABSOLUTE MAXIMUM RATINGS

| Supply voltage, V <sub>IN</sub>                                                                                    | -0.3V ~ 20.0V  |

|--------------------------------------------------------------------------------------------------------------------|----------------|

| Voltage at TX, RX, ADDRx, ISET, VDD, VIO, ADJR, FSMD                                                               | -0.3V ~6V      |

| Voltage at OUT1 to OUT12, FAULTB                                                                                   | +20V           |

| Maximum junction temperature, T <sub>JMAX</sub>                                                                    | +150°C         |

| Storage temperature range, TSTG                                                                                    | -65°C ~ +150°C |

| Operating temperature range, T <sub>A</sub> =T <sub>J</sub>                                                        | -40°C ~ +150°C |

| Package thermal resistance, junction to ambient (4-layer standard test PCB based on JESD 51-2A), $\theta_{JA}$     | 39.7°C/W       |

| Package thermal resistance, junction to thermal PAD (4-layer standard test PCB based on JESD 51-2A), $\theta_{JP}$ | 2.167°C/W      |

| ESD (HBM)                                                                                                          | ±2.5kV         |

| ESD (CDM)                                                                                                          | ±750V          |

**Note 3:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 7.2 ELECTRICAL CHARACTERISTICS

V<sub>IN</sub>= 12V, T<sub>J</sub>= T<sub>A</sub>= 25°C, unless otherwise noted. (Note 6)

| Symbol            | Parameter                      | Condition                                                      | Min. | Тур. | Max.  | Unit |

|-------------------|--------------------------------|----------------------------------------------------------------|------|------|-------|------|

| VIN               | Supply voltage                 |                                                                | 4.5  |      | 16    | V    |

| J                 | Maximum output current         | R <sub>ISET</sub> = 10kΩ, GCC= 0x3F,<br>SCAx= 0x7F, PWM= 0xFFF | 93.5 | 100  | 106.5 | mA   |

| Ιουτ              | Output current                 | R <sub>ISET</sub> = 33kΩ, GCC= 0x3F,<br>SCAx= 0x7F, PWM= 0xFFF | 27.9 | 30   | 32.1  | mA   |

| ΔΙ <sub>ΜΑΤ</sub> | IOUT mismatch (bit to bit)     | I <sub>OUT</sub> = 30mA                                        | -6.5 |      | 6.5   | %    |

| ΔΙΜΑΤ             | (Note 4)                       | Ιουτ= 100mA                                                    | -4.5 |      | 4.5   | %    |

| A                 | IOUT accuracy (device to       | Iout= 30mA                                                     | -5   |      | 5     | %    |

| ΔΙουτ             | device) (Note 5)               | Ιουτ= 100mA                                                    | -5   |      | 5     | %    |

| V                 | Headroom voltage               | Ιουτ= 100mA                                                    |      | 0.34 | 0.5   | V    |

| $V_{HR}$          | Headroom voltage               | Iout= 30mA                                                     |      | 0.2  | 0.4   | V    |

| lcc               | Quiescent power supply current | R <sub>ISET</sub> = 33kΩ, GCC= 0x3F,<br>SCAx= 0x7F, PWM= 0     | 3    | 4.5  | 6.5   | mA   |

| VISET             | ISET voltage                   | R <sub>ISET</sub> = 10kΩ, GCC= 0x3F,<br>SCAx= 0x7F, PWM= 0xFFF | 1.94 | 2.0  | 2.06  | V    |

| loz               | Output leakage current         | PWM= SL= GCC= 0, V <sub>OUT</sub> = 16V                        |      |      | 1     | μA   |

|                   |                                | Frequency setting= 24kHz,<br>8bit PWM mode                     | 21.6 | 24   | 26.4  | kHz  |

| fouт              | PWM frequency of output        | Frequency setting= 24kHz, 7+5bit PWM<br>mode, PWM>31/4096      | 21.6 | 24   | 26.4  | kHz  |

|                   |                                | Frequency setting= 244Hz,<br>12bit PWM mode                    | 219  | 244  | 269   | Hz   |

# **ELECTRICAL CHARACTERISTICS (CONTINUE)** $V_{IN}$ = 12V, $T_J$ = $T_A$ = 25°C, unless otherwise noted. (Note 6)

| Symbol                      | Parameter                                    | Condition                                                                                                                               | Min.                     | Тур. | Max.            | Unit |

|-----------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----------------|------|

| T <sub>SD</sub>             | Thermal shutdown                             |                                                                                                                                         |                          | 168  |                 | °C   |

| T <sub>SD_HYS</sub>         | Thermal shutdown<br>hysteresis               |                                                                                                                                         |                          | 15   |                 | °C   |

| Vpd_faultb                  | FAULTB pin pull-down<br>capability           | Isink= 2mA                                                                                                                              |                          | 0.1  | 0.2             | V    |

| Ilkg_faultb                 | FAULTB pin leakage current                   | V <sub>PULL-UP</sub> = 16V                                                                                                              |                          |      | 1               | μA   |

| VIH_RX                      | Logic "1" input voltage                      |                                                                                                                                         | 2                        |      |                 | V    |

| $V_{\text{IL}_{RX}}$        | Logic "0" input voltage                      |                                                                                                                                         |                          |      | 0.7             | V    |

| Vol(TX)                     | Low level output voltage                     | I <sub>SINK</sub> = 5mA                                                                                                                 |                          |      | 0.3             | V    |

| V <sub>OH(TX)</sub>         | High level output voltage                    | I <sub>SOURCE</sub> =5mA                                                                                                                | V <sub>IO</sub> -<br>0.3 |      | V <sub>IO</sub> | V    |

| $V_{\text{TH1\_AD/FS}}$     | ADDR0/ADDR1/FSMD<br>threshold1               |                                                                                                                                         | 0.9                      | 1    | 1.1             | V    |

| VTH2_AD/FS                  | ADDR0/ADDR1/ FSMD<br>threshold2              |                                                                                                                                         | 1.85                     | 2    | 2.15            | V    |

| VTH3_AD/FS                  | ADDR0/ADDR1/ FSMD<br>threshold3              |                                                                                                                                         | 2.8                      | 3    | 3.2             | V    |

| AD/FS                       | ADDR/FS source current                       |                                                                                                                                         | 46                       | 50   | 54              | μA   |

| $V_{\text{SC}_{\text{FL}}}$ | LED string short detection falling threshold | $R_{ISET}$ =33k $\Omega$ , GCC=0x3F, SCAx= 0x7F,<br>PWM=0xFFF, measured at V <sub>IN</sub> -V <sub>OUTx</sub><br>SHORT_FLT(4Bh) = "000" | 0.5                      | 1    |                 | v    |

| V <sub>SC_RS</sub>          | LED string short detection rising threshold  | $R_{ISET}$ =33k $\Omega$ , GCC=0x3F, SCAx= 0x7F,<br>PWM=0xFFF, measured at V <sub>IN</sub> -V <sub>OUTx</sub><br>SHORT_FLT(4Bh) = "000" |                          | 1.2  |                 | V    |

| $V_{\text{OC}\_\text{FL}}$  | LED string open detection falling threshold  | R <sub>ISET</sub> =33kΩ, GCC=0x3F, SCAx= 0x7F,<br>PWM=0xFFF, measured at OUTx                                                           | 50                       | 100  |                 | mV   |

| V <sub>OC_RS</sub>          | LED string open detection rising threshold   | R <sub>ISET</sub> =33kΩ, GCC=0x3F, SCAx= 0x7F,<br>PWM=0xFFF, measured at OUTx                                                           |                          | 167  |                 | mV   |

| V <sub>DD</sub>             | LDOOUT output voltage                        |                                                                                                                                         | 4.08                     | 4.2  | 4.32            | V    |

| Idd_max                     | LDOOUT output current<br>capability          | V <sub>IN</sub> > 4.5V, V <sub>DD</sub> > 3.8V                                                                                          |                          |      | 50              | mA   |

| I <sub>DD_LIM</sub>         | LDOOUT output current limit                  | V <sub>IN</sub> = 12V, V <sub>DD</sub> = 0V                                                                                             | 60                       |      |                 | mA   |

| Vdd_uv                      | LDOOUT undervoltage-<br>lockout threshold    | Voltage falling, IC disabled                                                                                                            |                          | 3.7  |                 | V    |

| VDD_UVHY                    | VDD undervoltage-<br>lockout hysteresis      |                                                                                                                                         |                          | 100  |                 | mV   |

### ELECTRICAL CHARACTERISTICS (CONTINUE)

$V_{IN}$ = 12V, T<sub>J</sub>= T<sub>A</sub>= 25°C, unless otherwise noted. (Note 6)

| Symbol               | Parameter                                | Condition                   | Min.  | Тур. | Max.  | Unit |

|----------------------|------------------------------------------|-----------------------------|-------|------|-------|------|

| $\Delta I_{ICTRL_1}$ | I minmetch (bit to bit)                  | V <sub>ADJ</sub> = 0.6V     | -3    |      | 3     | %    |

| $\Delta I_{ICTRL_2}$ | lout mismatch (bit to bit)               | V <sub>ADJ</sub> = 1.4V     | -3    |      | 3     | %    |

| Vslsth               | Single LED short detect threshold        | SLSTH (41h~49h) = "0010"    |       | 3.9  |       | V    |

| VF_UVLO              | Single LED short/String open detect UVLO | FS_FLTL (4Bh) = "00000100"  |       | 8    |       | V    |

| VIO                  | TX power supply                          |                             | 3     |      | 5.5   | V    |

| V <sub>VIN_UV</sub>  | VIN undervoltage-lockout<br>threshold    | Voltage falling, IC disable |       | 3.7  |       | V    |

| Vvin_uvhy            | VIN undervoltage-lockout<br>hysteresis   |                             |       | 100  |       | mV   |

| fosc                 | System clock frequency                   |                             | 32.34 | 33   | 33.66 | MHz  |

**Note 4:**  $I_{OUT}$  mismatch (bit to bit)  $\triangle I_{MAT}$  is calculated:

$$\Delta I_{MAT} = MAX \left( ABS \left( \frac{I_{OUTn} (n = 1 \sim 12)}{\frac{I_{OUT1} + I_{OUT2} + \dots + I_{OUT12}}{12}} - 1 \right) \right) \times 100\%$$

Note 5:  $I_{\text{OUT}}$  accuracy (device to device)  $\bigtriangleup I_{\text{OUT}}$  is calculated:

$$\Delta I_{OUT} = ABS \left( \frac{I_{OUT1} + I_{OUT2} + \dots + I_{OUT12}}{12} - I_{OUT(TYP)}}{I_{OUT(TYP)}} \right) \times 100\%$$

When  $R_{ISET}=10k\Omega$ ,  $I_{OUT(TYP)}=100mA$ ; and when  $R_{ISET}=33k\Omega$ ,  $I_{OUT(TYP)}=30mA$ .

**Note 6:** Production testing of the device is performed at 25°C.

Note 7: Guaranteed by design.

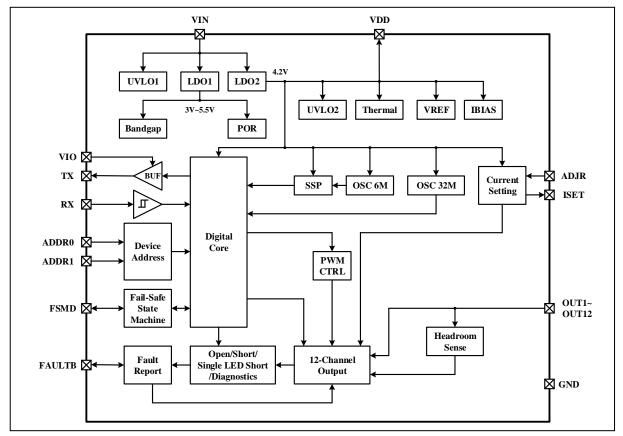

### 8 FUNCTIONAL BLOCK DIAGRAM

### 9 APPLICATION INFORMATION

### 9.1 OVERVIEW

The IS32LT3137 is an automotive 12-channel LED driver with a UART interface for individual control of each LED string. Each channel is a constant current sink capable of up to 100mA and supports both DC adjustment and PWM dimming. The output current and PWM duty cycle of each channel can be individually configured through the UART interface. For high current LED applications, multiple output channels can be combined in parallel.

For added system reliability, the IS32LT3137 features various fault protections, including LED string open, LED string shorted, single LED shorted, overcurrent (ISET pin shorted), over temperature, CRC error and watchdog timeout (fail-safe modes) conditions for robust operation. Detection of these failures is reported by a dedicated reporting pin, FAULTB. There are also dedicated flag bits in registers for each failure which can be read back by the external host MCU through the interfaces. To optimize EMI performance, the IS32LT3137 features spread spectrum on the internal PWM base clock to spread the total electromagnetic emitting energy into a wider range that significantly degrades the peak energy of EMI. In addition, the output current source ON/OFF transitions during PWM dimming have a slew rate control and programmable phase delay to mitigate EMI and power supply inrush current.

The IS32LT3137 interface is UART, and it supports up to 16 slave IS32LT3137 devices. The device address can be configured by the three address pins. The UART receives data to control all output channels and sends back fault information to the host MCU. The UART interface in conjunction with an external standard CAN transceiver enables long distance communication with a host MCU placed outside of the lamp module (as shown in Figure 4). Based on the CAN physical layer, it achieves excellent EMC and EMI performance. The embedded CRC correction of the UART data stream can ensure robust communication in automotive environments. The UART interface is easily supported by most MCUs in the market.

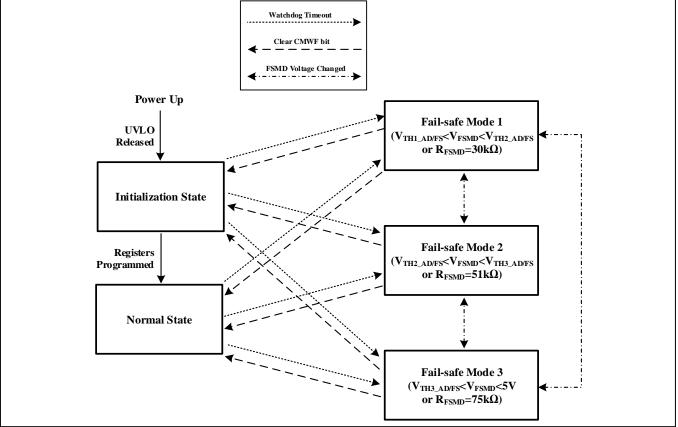

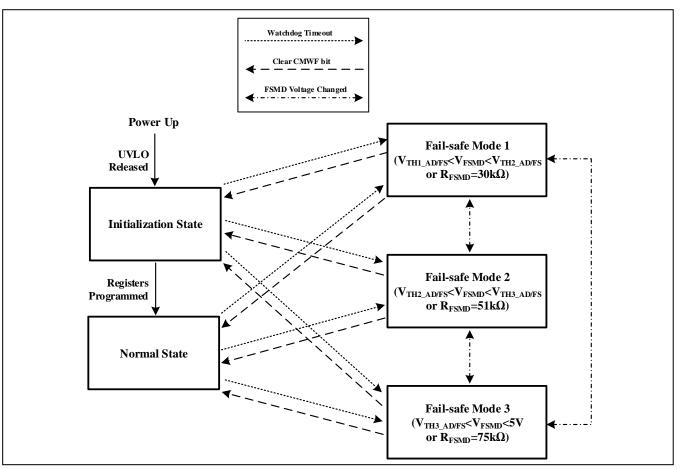

To further increase robustness, the fail-safe mode of the device allows automatic switching to fail-safe state in case of the communication loss, for example, host MCU failure or communication cables broken. The device supports different fail-safe modes configured by the FSMD pin.

Figure 4 UART Interface with External CAN Transceiver for Outside Module Long Distance Communication

### 9.2 POWER SUPPLY

### 9.2.1 VIN UNDERVOLTAGE-LOCKOUT (UVLO)

The IS32LT3137 features an undervoltage-lockout (UVLO) function on the VIN pin to prevent unintended operation at too low supply voltages. UVLO threshold is an internally fixed value and cannot be adjusted. Entering UVLO will reset all registers to their default value. The device is disabled when the VIN voltage drops below  $V_{VIN_UV}$  and automatically resumes normal operation when the VIN voltage rises above ( $V_{VIN_UV} + V_{VIN_UVHY}$ ).

### 9.2.2 INTERNAL 4.2V LINEAR REGULATOR (VDD)

The IS32LT3137 device integrates an internal linear regulator (LDO) with 4.2V (Typ.) and  $I_{DD\_MAX}$  current capability to provide power supply to the internal analog and digital circuits. During operation, the internal circuitry can be subject to transient currents from this linear regulator. Therefore, a 4.7µF low ESR, X7R type ceramic capacitor is necessary from VDD pin to GND, it must be placed as close to the VDD pin as possible. This linear regulator also has the UVLO feature. The device is disabled when the V<sub>DD</sub> voltage drops below V<sub>DD\_UV</sub> and resumes normal operation when the VDD voltage rises above (V<sub>DD\_UV</sub>). Entering UVLO will reset all registers to their default value. An I<sub>DD\_LIM</sub> current limit on VDD pin protects the IS32LT3137 from VDD output overload or short-circuit conditions.

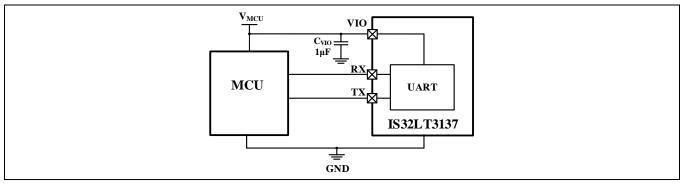

### 9.2.3 VIO VOLTAGE SUPPLY

The positive voltage rail of the UART interface is supplied with the VIO pin which must be connected to a proper voltage source. Usually, the VIO pin should be connected to the same power supply as the MCU. If a 5V MCU is used for IS32LT3137 control, the VIO pin can be directly connected to the VDD pin.

Figure 5 VIO Voltage Supply

### 9.3 OUTPUT CURRENT SETTING

The full DC output current ( $I_{OUT_FU}$ ) for each channel is set with resistor ( $R_{ISET}$ ) connected from the ISET pin to GND. This current set resistor is computed using the following equation:

If the CM bit in the CONFIG register (00h) is set to "0":

$$I_{OUT\_FU} = \frac{V_{ISET}}{R_{ISET}} \times 500 \tag{1}$$

Where VISET is the voltage of ISET pin, when VADJ is lower than 2V (Typ.),

$$I_{OUT\_FU} = \frac{V_{ADJ}}{R_{ISET}} \times 500$$

(2)

$(10k\Omega \le R_{ISET} \le 75k\Omega)$

If the CM bit in the CONFIG register (00h) is set to "1":

$$I_{OUT\_FU} = \frac{V_{ISET}}{R_{ISET}} \times 165$$

(3)

Where VISET is the voltaeg of ISET pin, when VADJ is lower than 2V (Typ.),

$$I_{OUT\_FU} = \frac{V_{ADJ}}{R_{ISET}} \times 165$$

(4)

$(10k\Omega \le R_{ISET} \le 75k\Omega)$

It is recommended that R<sub>ISET</sub> be a 1% accuracy resistor with good temperature characteristic to ensure stable output current. R<sub>ISET</sub> must be placed as close to ISET pin as possible on PCB layout to avoid noise interference and ground bounce. The device is protected from an output overcurrent condition caused by R<sub>ISET</sub> resistor. The output current is reduced to 17mA (Typ.) if the ISET pin is shorted to ground or R<sub>ISET</sub> resistor value is too low.

When  $R_{ISET}$  is fixed, the DC output current for each channel can be further adjusted in 64-steps by the GCC[5:0] bits in the GC\_CTRL register (01h). Furthermore, based on the GCC[5:0] setting, each channel also supports individual 128-step programmable DC output current adjustment. This feature can be used to set binning values for output LEDs or to calibrate the LEDs to achieve high brightness homogeneity based on an external visual calibration system to further save binning cost. The 7-bit Scaling Registers SCAx (14h~1Fh) individually set the DC output current of each channel.

GCC[5:0] and SCAx control the OUTx current  $(I_{OUTx})$  as shown in following equation:

$$I_{OUTx} = I_{OUT\_FU} \times \frac{GCC}{64} \times \frac{SCAx}{128}$$

(5)

Where, x is from 1 to 12 for different output channel.

$$GCC = \sum_{n=0}^{5} D[n] \cdot 2^{n}$$

(6)

$$SCAx = \sum_{n=0}^{6} D[n] \cdot 2^n \tag{7}$$

For example: assume GCC[5:0] = 0x05 and SCA1 = 0x40. GCC = 5. Then the DC output current of OUT1 is:

$$I_{OUT1} = I_{OUT\_FU} \times \frac{5}{64} \times \frac{64}{128}$$

If any channel(s) are unused, please connect the corresponding OUTx pin(s) to the GND pin to avoid false fault detection and set the corresponding PWM and scaling registers to "0x00" to turn off these output(s).

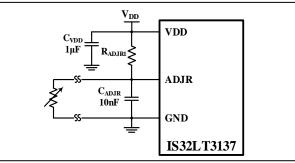

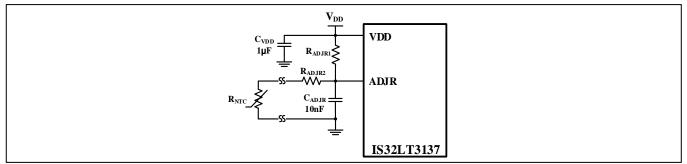

### 9.4 ANALOG DIMMING

The IS32LT3137 offers an analog dimming input pin, ADJR. The dimming voltage range of ADJR pin is 0.06V to 2V. The global output current can be regulated by the ADJR pin voltage. If the analog dimming pin ADJR is pulled up above 2V, analog dimming is disabled, and the output current is 100% (full current). When the ADJR pin is driven below 2V, the analog dimming is enabled, and the pin voltage (0.06~2V) will proportionally control the output current.

Figure 6 IS32LT3137 Analog Dimming for LED Binning

Figure 7 IS32LT3137 Analog Dimming for Thermal Roll-off

The ADJR pin can be used to fine tune the output current for LED binning during mass-production. The ADJR pin can also be used in conjunction with an NTC thermistor to provide over temperature current roll-off protection for the LED load or the system. As shown in Figure 6 and Figure 7, the IS32LT3137 can perform either LED binning or thermal roll-off function, not both at the same time.

### 9.5 PWM DIMMING

The IS32LT3137 integrates independent 12-bit PWM generators for each output channel. The output current for each channel is turned on and off as controlled by the PWM generator. The average current of each output channel can be adjusted by it's PWM duty cycle to control the LED channel brightness. The PWM Registers (26h~36h) individually set the PWM duty cycle for each channel.

The PWM dimming frequency is programmable by the CONFIG register (00h). The maximum PWM frequency can be up to 24kHz (Typ.). Due to the output current slew rate control, a high frequency PWM signal has a shorter period time that will degrade the PWM dimming linearity. Therefore, a low frequency PWM signal is good for achieving better dimming contrast ratio. At a 100Hz~500Hz PWM frequency, the dimming duty cycle can be varied from 100% down to 1% or lower. Select the PWM dimming frequency based on the minimum brightness requirement for the application.

The PWM generators dim the LEDs by its duty cycle:

$I_{OUTx\_PWM} = I_{OUTx} \times D_{PWMx}$ (8)

Where, D<sub>PWMx</sub> is duty cycle of each channel independently programmed by PWM Registers (26h~40h), in 12bit or 7+5-bit PWM mode:

$$D_{PWMx} = \frac{\sum_{n=0}^{11} D[n] \cdot 2^n}{4096}$$

(9)

In 8bit PWM mode:

$$D_{PWMx} = \frac{\sum_{n=4}^{11} D[n] \cdot 2^n}{256}$$

(10)

### 9.5.1 PWM SPREAD SPECTRUM

The IS32LT3137 includes a spread spectrum feature on PWM base clock to optimize EMI performance. The spread spectrum function helps spread the total electromagnetic emitting energy into a wider range that significantly degrades the peak energy of EMI. With spread spectrum, the EMI test can be passed with smaller size and lower cost filter circuit. Spread spectrum is enabled/disabled by the SSCCFG register (4Ah).

### 9.5.2 PWM PHASE DELAY

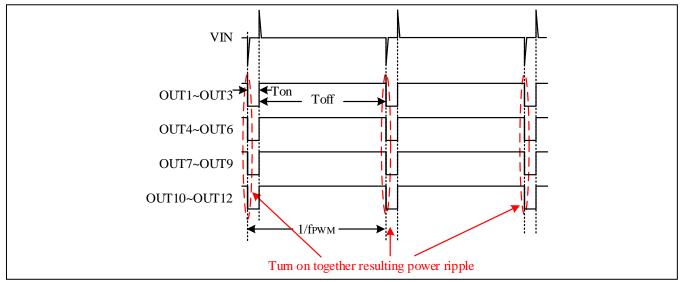

To mitigate transient current generation and power supply ripple, the IS32LT3137 features PWM phase delay. When PWM phase delay is disabled (PHASE\_CTRL(03h) is set to "0x00", default value is 0x01 phase delay enable), all channels are simultaneously turned on at the beginning of each PWM cycle. This will result in large current draw from power supply leading to high voltage ripple on the power supply rail. As shown in figure 8.

Figure 8 PWM Phase Delay Disabled

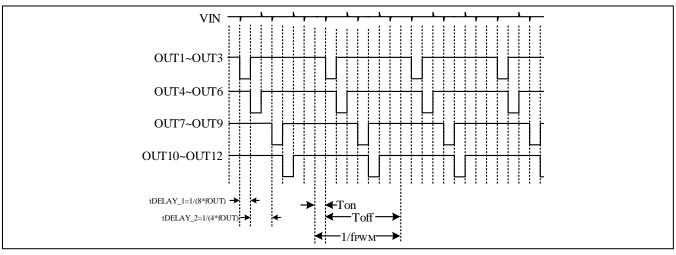

The IS32LT3137 divides 12 output channels into 4 groups to perform PWM phase delay, OUT1&OUT2&OUT3 as group 1, OUT4&OUT5&OUT6 as group 2, ...OUT10&OUT1&OUT12 as group 4. When the PDE bit in the PHASE\_CTRL register (03h) is set to "1", the phase delay is enabled, starting each group in turn from each PWM cycle. The  $t_{DELAY_1}$  is interval delay time between group 1 & group 2, group 3 & group 4, and  $t_{DELAY_1}$  is 1/8 PWM cycle (1/ $f_{PWM}$ ). The  $t_{DELAY_2}$  is interval delay time between group 2 & group 3, and  $t_{DELAY_2}$  is 1/4 PWM cycle (1/ $f_{PWM}$ ). This minimizes the voltage ripple on the VIN power supply rail. As shown in figure 9.

Figure 9 PWM Phase Delay Enabled

### 9.6 FAULT PROTECTION

### 9.6.1 FAULT REPORTING

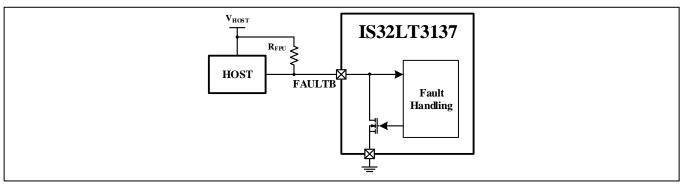

For added system reliability, the IS32LT3137 integrates various fault detections for LED string open/short, single LED short, overcurrent (ISET shorted), over temperature, CRC error and watchdog timeout (fail-safe modes) conditions. The open drain pin FAULTB can be used for fault condition reporting. If any fault occurs, the corresponding bit in FLT\_TYPE register will be set to "1" and the FAULTB pin will go low after a delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report fault condition. When it's monitored by a host MCU, a pull-up resistor  $R_{FPU}$  (10k $\Omega$  recommended) from the FAULTB pin to the supply of the host MCU is required.

Figure 10 Host Monitors the Fault Reporting

### 9.6.2 LED STRING OPEN PROTECTION

The LED string open detection is enabled by setting the ODE and ODF bits in FLT\_DET\_EN register (4Ch) to "1". If any LED string is opened, the corresponding OUTx pin voltage will be pulled down close to zero. When the OUTx pin voltage,  $V_{OUTx}$ , falls below the LED string open detection voltage,  $V_{OC_{FL}}$  and persists for longer than a deglitch time (typical 10µs), the LED string open protection will be triggered. The corresponding fault flag bits in OPEN\_FLT register (51h & 52h) and the OPENF bit in FAULT\_TYPE register (57h) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The faulty channel will reserve a 4mA retry current for recovery detection.

No matter in which fault protection mode, the device will recover to normal operation and the FAULTB pin will go back to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) expires once the open condition is removed, i.e. V<sub>OUTx</sub> rising above the LED string open detection voltage, V<sub>OC\_RS</sub>. The corresponding fault flag bit in OPEN\_FLT register will reset to "0". However, the OPENF bit in FAULT\_TYPE register (57h) is latched, which means that it cannot automatically reset to "0" after open condition being removed but must be cleared by the host MCU writing it back to "0".

When PWM dimming is implemented, the LED string open detection is only enabled during the PWM ON phase. If the PWM on-time is less than the deglitch time (typical 10µs), the device does not report any LED string open fault.

### 9.6.3 LED STRING SHORT PROTECTION

The LED string short detection is enabled by setting the SDE and SDF bits in FLT\_DET\_EN register (4Ch) to "1". If any LED string is short, the corresponding OUTx pin will be pulled up close to V<sub>IN</sub>. When dropout voltage from the VIN pin to the OUTx pin, V<sub>IN</sub>-V<sub>OUTx</sub> (when SHORT\_FLT(4Bh) = "000"), rises above the LED string short detection voltage, V<sub>SC\_RS</sub>, and persists for longer than a deglitch time (typical 10µs), the LED string short protection will be triggered. The corresponding fault flag bits in SHORT\_FLT register (4Eh & 4Fh) and the SHORTF bit in FAULT\_TYPE register (57h) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The faulty channel will reserve a 4mA retry current for recovery detection.

No matter in which fault protection mode, the device recovers to normal operation and the FAULTB pin will go back to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the short condition is removed,  $V_{OUTx}$  falling above the LED string short detection voltage,  $V_{SC_FL}$ . The corresponding fault flag bit in SHORT\_FLT register will reset to "0". However, the SHORTF bit in FAULT\_TYPE register (57h) is latched, which means that it cannot automatically reset to "0" after short condition being removed but must be cleared by the host MCU writing it back to "0".

When PWM dimming is implemented, the LED string short detection is only enabled during PWM ON phase. If the PWM on-time is less than the deglitch time (typical 10µs), the device does not report any LED string short fault.

When the device is operated in DC mode, the PWM function is disabled. It is recommended to not enable both LED string short and single LED short, because the IS32LT3137 may incorrectly report an LED string short as a single LED short. Individually enable either LED string short or single LED short detection. If a single LED short is reported, double check for LED string short or single LED short in software.

### 9.6.4 SINGLE LED SHORT PROTECTION

The single LED short detection is enabled by setting the SLSDE and SLSDF bits in FLT\_DET\_EN register (4Ch) to "1". Then the single LED short detection is active after VIN voltage rising above the fault undervoltage-lockout voltage threshold  $V_{FLT_UV}$ . That helps to prevent false fault detection due to the insufficient power supply voltage, such as power up transience. The single LED short detect threshold  $V_{SLSTH}$  of each channel is individually programmed by the corresponding LEDx\_SLS[4:0] bits in LEDx\_SLSTH registers (41h~46h). If single LED of any string is shorted, the corresponding OUTx pin voltage will rise. When the OUTx pin voltage,  $V_{OUTx}$ , rise above single LED short detect threshold,  $V_{SLSTH}$ , and persists for longer than a deglitch time (typical 10µs), the single LED short protection will be triggered. The corresponding fault flag bits in SLS\_FLT register (54h & 55h & 56h) and the SLS\_FLT bit in FAULT\_TYPE register (57h) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The faulty channel will reserve a 4mA retry current for recovery detection.

The device recovers to normal operation and the FAULTB pin will go back to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the single LED short condition is removed, V<sub>OUTx</sub> rising above the LED string short detection voltage, V<sub>SLSTH</sub>. The corresponding fault flag bit in SLS\_FLT register will reset to "0". However, the SLSHORTF bit in FAULT\_TYPE register (57h) is latched, which means that it cannot automatically reset to "0" after single LED short condition being removed but must be cleared by the host MCU writing it back to "0".

When PWM dimming is implemented, the single LED string short detection is only enabled during PWM ON phase. If the PWM on-time is less than the deglitch time (typical 10µs), the device does not report any single LED short fault.

### 9.6.5 OUTPUT OVERCURRENT (ISET PIN SHORT)

The device is protected from an output overcurrent condition caused by the  $R_{ISET}$  resistor. All output current is limited to 110mA (Typ.) in case of the ISET pin shorted to ground or too low value  $R_{ISET}$  resistor is connected to ISET pin. If the condition persists for longer than a deglitch time (typical 1µs), the ISET pin short protection will be triggered. All output current will be reduced to 17mA (Typ.). The RSET\_SH bit in FAULT\_TYPE register (57h) will be set to "1" and the FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition.

Once the resistance from the ISET pin to GND resumes to a normal range, all channels will recover to normal operation and the FAULTB pin will recover to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register). However, the RSET\_SH bit in FAULT\_TYP register (57h) is latched, which means that it cannot automatically reset to "0" after ISET short condition being removed but must be cleared by the host MCU writing it back to "0".

### 9.6.6 THERMAL SHUTDOWN

If the junction temperature exceeds  $T_{SD}$  (Typ. 168°C), all output channels will go to the OFF state and the TSD bit in FAULT\_TYPE register (57h) will be set to "1". If the TRE bit in TEMP\_SEN register (02h) to "1", the FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. At this point, the device presumably begins to cool off. Any attempt to toggle the channels back to the source condition before the device has cooled to below ( $T_{SD}-T_{SD_HYS}$ ) (Typ. 155°C) will be blocked and the device will not be allowed to restart. The FAULTB pin will recover to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the device cools down. However, the TSD bit in FAULT\_TYPE register (57h) is latched, which means that it cannot automatically reset to "0" but must be cleared by the host MCU writing it back to "0".

### 9.6.7 THERMAL ROLL-OFF PROTECTION

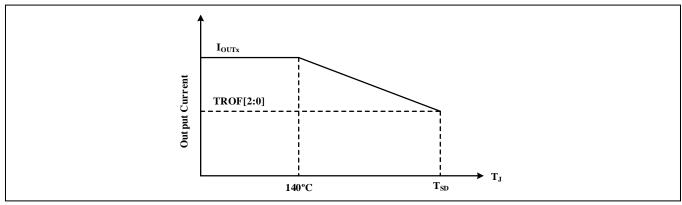

The device integrates the thermal shutdown protection to prevent the device from overheating. In addition, to prevent the LEDs from flickering due to rapid thermal changes, the device also includes a programmable thermal roll-off feature to reduce power dissipation at high junction temperature.

The output current will be equal to the set value  $I_{OUTx}$  if the junction temperature of the device remains below thermal roll-off temperature threshold 140°C. If the junction temperature exceeds the temperature threshold, the output current of all channels will begin to linearly reduce following the junction temperature ramping up until thermal

shutdown. The TF bit in FAULT\_TYPE register (57h) will be set to "1". If the TRRE bit in TEMP\_SEN register (02h) to "1", the FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The percentage of the output current before thermal shutdown is programmable by the TROF[2:0] bits in the TEMP\_SEN register (02h).

The output current will linearly resume to the set value  $I_{OUTx}$  and the FAULTB pin will recover to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the junction temperature cools down below the thermal roll-off temperature threshold 140°C. However, the TF bit in FAULT\_TYPE register (57h) is latched, which means that it cannot automatically reset to "0" but must be cleared by the host MCU writing it back to "0".

Figure 11 Thermal Roll-off Protection

By mounting the IS32LT3137 device on the same thermal substrate as the LEDs, use of this feature can also limit the dissipation of the LEDs.

### Fault Action Table (Both Normal State And Fail-Safe State)

| Fault Type                      | Detection                                                                                                                                                                                                                                                        | Conditions                                                              | Actions                                                                 | Fault Flags                        | FAULTB<br>Pin          | Recovery                                                                                                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply UVLO                     | Vin <vvin_uv<br>or<br/>Vdd<vdd_uv< td=""><td>-</td><td>Turn off all<br/>channels and reset<br/>all registers to<br/>default value</td><td>-</td><td>No action</td><td>Vin&gt;(Vvin_uv+Vvin_uvhy)<br/>or<br/>Vdd&gt;(Vdd_uv+Vdd_uvhy)</td></vdd_uv<></vvin_uv<br> | -                                                                       | Turn off all<br>channels and reset<br>all registers to<br>default value | -                                  | No action              | Vin>(Vvin_uv+Vvin_uvhy)<br>or<br>Vdd>(Vdd_uv+Vdd_uvhy)                                                                                                                      |

| LED string open                 | V <sub>IN</sub> >V <sub>FLT_UV</sub><br>and<br>V <sub>OUTx</sub> <v<sub>OC_FL</v<sub>                                                                                                                                                                            | PWM pulse width greater<br>than 10µs (Typ.) and<br>ODE = 1, ODF = 1     | Faulty channel<br>outputs 4mA and<br>other channels on<br>(ODF = 1)     | OPEN_FLT<br>and<br>OPENF bit       | Pull low               | V <sub>OUTx</sub> >V <sub>OC_RS</sub><br>Write OPENF bit to "0"                                                                                                             |

| LED string short                | (V <sub>IN</sub> - V <sub>OUTx</sub> )<br><v<sub>SC_RS<br/>(SHORT_FLT=0<br/>00) or<br/>V<sub>OUTX</sub> &gt; V<sub>SC</sub><br/>(SHORT_FLT≠0<br/>00)</v<sub>                                                                                                     | PWM pulse width greater<br>than 10µs (Typ.) and<br>SDE = 1, SDF = 1     | Faulty channel<br>outputs 4mA and<br>other channels on<br>(SDF = 1)     | SHORT_FLT<br>and<br>SHORTF bit     | Pull low               | (V <sub>IN</sub> - V <sub>OUTx</sub> ) >V <sub>SC_FL</sub><br>(SHORT_FLT=000)<br>or<br>V <sub>OUTX</sub> < V <sub>SC</sub><br>(SHORT_FLT≠000)<br>Write SHORTF bit to<br>"0" |

| Single LED<br>short             | Vin>Vflt_uv<br>and<br>Voutx>Vslsth                                                                                                                                                                                                                               | PWM pulse width greater<br>than 10µs (Typ.) and<br>SLSDE = 1, SLSDF = 1 | Faulty channel<br>outputs 4mA and<br>other channels on<br>(SLSDF = 1)   | SLST_FLT<br>and<br>SLSHORTF<br>bit | Pull low               | V <sub>OUTx</sub> <v<sub>SLSTH<br/>Write SLSHORTF bit to<br/>"0"</v<sub>                                                                                                    |

| ISET pin short<br>(Overcurrent) | l <sub>o∪⊤x</sub> limited to<br>110mA (Typ.)                                                                                                                                                                                                                     | Longer than 1µs (Typ.)<br>deglitch time                                 | All channels<br>reduced to 17mA<br>(Typ.)                               | RSET_SH bit                        | Pull low               | ISET pin to GND<br>resistance resumes to<br>normal range,<br>Write RSET_SH bit to<br>"0"                                                                                    |

| Thermal shutdown                | TJ>Tsd                                                                                                                                                                                                                                                           | -                                                                       | All channels off                                                        | TSD bit                            | Pull low<br>(TRE = 1)  | T <sub>J</sub> <(T <sub>SD</sub> -T <sub>SD_HYS</sub> )<br>Write TSD bit to "0"                                                                                             |

| Thermal roll-off                | TJ>140°C                                                                                                                                                                                                                                                         | TROF[2:0] ≠ 00                                                          | All channels<br>linearly reduce<br>output current                       | TF bit                             | Pull low<br>(TRRE = 1) | TJ<140℃<br>Write TF bit to "0"                                                                                                                                              |

| CRC error                       | Calculated CRC<br>does not match<br>CRC data                                                                                                                                                                                                                     | -                                                                       | Increments CRC<br>Error Count<br>register                               | CRCF bit                           | Pull low               | Write CRCF bit to "0"                                                                                                                                                       |

| Communication<br>loss           | Watchdog<br>times out                                                                                                                                                                                                                                            | $R_{FSMD}$ =30kΩ, 51kΩ or<br>75kΩ and no error-free<br>communication    | Enter fail-safe<br>modes                                                | CMWF bit                           | Pull low               | Write CMWF bit to "0"                                                                                                                                                       |

Note 8: OPENF, SHORTF, SLSHORTF, ISETSF, TSD, TF, CMWF and CRCF bits are latched. Even though the fault conditions are removed, they cannot automatically reset to "0" but must be cleared by the host MCU writing it back to "0".

### 9.7 UART INTERFACES

The host MCU can communicate with the IS32LT3137 device using a Universal Asynchronous Receiver and Transmitter (UART). The UART communication process uses a command and response protocol mastered by the host MCU to write and read the registers to and from each IS32LT3137 device. The IS32LT3137 UART interface utilizes half-duplex communications (transmit and receive cannot overlap). A tri-state buffer in the IS32LT3137 drives the TX out pin, so it is recommended to place an external pull-up resistor on the RX input return line of the host MCU. An external pull-up on the MCU TX output will allow multiple IS32LT3137 devices to share a common pair of TX and RX signals by connecting all IS32LT3137 TX lines together and all IS32LT3137 RX lines together. The baud rate can support 100kbps~1Mbps.

Figure 12 UART Interface Connection

Additionally, the physical TX and RX connections of IS32LT3137 can be joined together through a standard CAN transceiver (CAN PHY), as shown in Figure 13. This has the added advantage of protection from shorts to battery and/or shorts to ground on the cables and/or harnesses between the host MCU board and the IS32LT3137 board. The CAN physical layer has excellent EMI and EMS performance with long distance off-board connection.

Figure 13 UART Interface with Standard CAN Transceiver Connection

### 9.7.1 UART DATA FORMAT

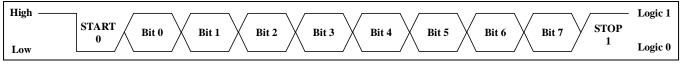

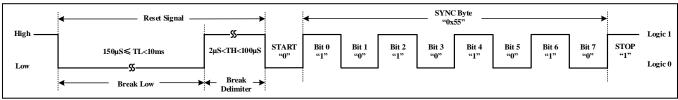

Figure 14 UART Data Byte Format

The UART operates with one start bit, eight data bits (LS bit first) and one stop bit. Above figure shows the waveform for an individual byte transfer on the UART. A logic "1" state occurs when the device drives the line to high voltage. A logic "0" state occurs when the device drives the line to ground. Below figure shows actual data bytes with UART data format.

|        |              | ← 0xD9       |              |              |              |              |              |              |              |             |           |

|--------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-----------|

| High — | START        | Bit 0        | Bit 1        | Bit 2        | Bit 3        | Bit 4        | Bit 5        | Bit 6        | Bit 7        | GTOD        | · Logic 1 |

| Low    | "0"          | "1"          | "0"          | "0"          | "1"          | "1"          | "0"          | "1"          | "1"          | STOP<br>"1" | Logic 0   |

| High — | START<br>"0" | Bit 0<br>"0" | Bit 1<br>"1" | Bit 2<br>"1" | Bit 3<br>"0" | Bit 4<br>"0" | Bit 5<br>"1" | Bit 6<br>"0" | Bit 7<br>"0" | STOP<br>"1" | Logic 1   |

| Low    |              |              |              |              |              |              |              |              |              | Logic 0     |           |

The baud rate of UART communication can be 100kbps to 1Mbps which is synchronized by the baud rate of the SYNC byte of the BUS Reset command. The UART uses 32x over-sampling on the incoming asynchronous RX signal. Between UART data bytes, at least one bit is required as STOP bit.

### 9.7.2 COMMUNICATION PROTOCOL

The communication process of all three interfaces uses a command and response protocol mastered by the host MCU to write and read the registers to and from each IS32LT3137 device. This means that the IS32LT3137 device never initiates traffic onto the network. The protocol maps the registers into an address space on each device. The host MCU uses the protocol to initiate a communication transaction by sending a command frame. This command frame addresses either one IS32LT3137 device directly or broadcasts to all IS32LT3137 devices on the network. This addressing may cause a response frame to be sent back from the slave IS32LT3137 device depending on the command type of the command frame. There are four types of commands:

- 1) BUS Reset Command: resets the UART

- 2) Write Command: writes data from host MCU to specific IS32LT3137 device(s)

- 3) Read Command: reads data from specific IS32LT3137 device to host MCU

- 4) Special Command: specifies IS32LT3137 device(s) to implement specific function.

There is no response frame given following a broadcast write command frame. Therefore, only two types of response frames exist that an IS32LT3137 device sends back to the host MCU: Write Acknowledge (if enabled) and Read Response.

### 9.7.3 COMMAND FRAME TYPES

### 9.7.3.1 BUS Reset Command Frame

The host MCU can reset the device UART and protocol state machine at any time by sending BUS Reset command. The BUS Reset command consists of reset signal and SYNC byte (0x55). The reset signal includes at 150µs~10ms break low and at 2µs~100us logic high break delimiter. Upon receiving the bus reset signal, the state machine of all IS32LT3137 devices on the bus will be reset to a known-good state. The bus reset signal must be followed by a SYNC byte (0x55) send by desired baud rate (within 100kbps to 1Mbps) to synchronize the baud rate to all IS32LT3137 devices. The subsequent communication must use the identical baud rate. With this synchronization approach, the cost of an external crystal oscillator is saved. To avoid clock drift over time and ambient temperature, it's recommended to periodically send a BUS Reset Command to the IS32LT3137 devices.

Figure 16 BUS Reset Command

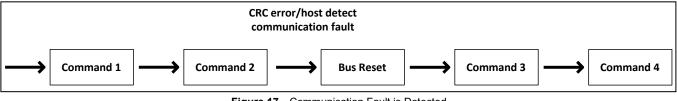

Upon system power up, the host MCU must initialize the BUS by sending a BUS Reset Command before communication. This BUS reset operation can be optionally performed by the host MCU for several application scenarios: (1) upon system power up, (2) communication watchdog times out, (3) communication fault is detected, illustrated as in the following diagram:

Figure 17 Communication Fault is Detected

Note that the BUS Reset command only resets the interface state machine (including stored communication baud rate). It does not reset the registers and does not halt normal LED PWM operation.

Note 9: If TX or RX anyone disconnect, there will cause CRC error, communication again need send Bus reset.

#### 9.7.3.2 Write Command Frame

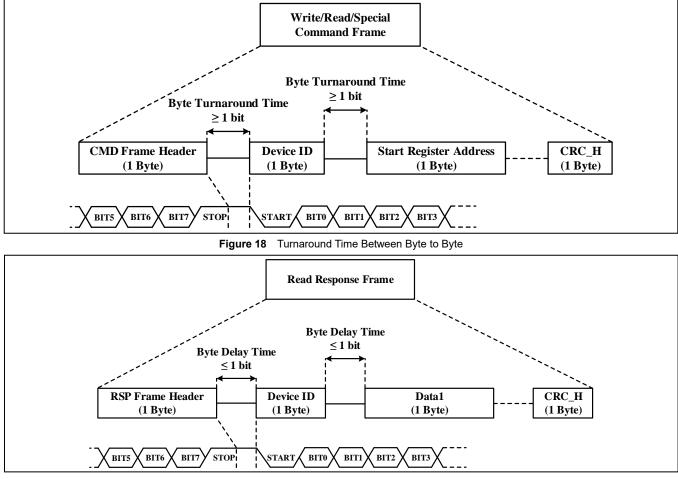

The Write Command Frame is comprised of the following sequence.

| H | ) Frame<br>eader<br>e Byte) | Device ID<br>(One Byte) | Start Register<br>Address<br>(One Byte) | Data 1<br>(One Byte) |  | Data N<br>(One Byte) | CRC_L<br>(One Byte) | CRC_H<br>(One Byte) |

|---|-----------------------------|-------------------------|-----------------------------------------|----------------------|--|----------------------|---------------------|---------------------|

|---|-----------------------------|-------------------------|-----------------------------------------|----------------------|--|----------------------|---------------------|---------------------|

#### 9.7.3.3 Acknowledge Frame

If the ACKEN bit is set in the SYSCFG register, the addressed device transmits an acknowledge back to the host MCU upon a successful single device write. The Acknowledge Frame is comprised of a single byte (ACK=0x7F) as the following sequence.

| ACK    |  |

|--------|--|

| (0x7F) |  |

#### 9.7.3.4 Read Command Frame (transferred by the host MCU)

The Read Command Frame is comprised of the following sequence.

| CMD Frame Header | Device ID  | Start Register Address | CRC_L      | CRC_H      |

|------------------|------------|------------------------|------------|------------|

| (One Byte)       | (One Byte) | (One Byte)             | (One Byte) | (One Byte) |

| (= ))            | (= ))      | (= <b>J</b> )          | (= ))      | ( = J )    |

A successfully-addressed IS32LT3137 device then transfers back the appropriate Read Response Frame.

The Read Response Frame is comprised of the following sequence.

| RSP Frame Header Device ID | Data 1     | <br>Data N | CRC_L      | CRC_H      |

|----------------------------|------------|------------|------------|------------|

| (One Byte) (One Byte)      | (One Byte) | (One Byte) | (One Byte) | (One Byte) |

#### 9.7.3.5 **Special Command Frame**

The special command specifies the IS32LT3137 device to implement specific function which includes:

a) Update Command

This special command is used for below scenarios:

- Update the configuration of the PWM registers data and Scaling registers data into output stages at the next PWM boundary after this command is issued.

- Update the configuration of the DC\_PWM\_SEL register (00h).

- Update the configuration of the PHASE\_CTRL register (03h).

- b) Registers Reset Command

Resets all registers to default value, excluding the PWR bit in SYSCFG register (4Ah).

The Special Command Frame is comprised of the following sequence:

| CMD Frame Header | Device ID  | CRC L      | CRC H      |

|------------------|------------|------------|------------|

| (One Byte)       | (One Byte) | (One Byte) | (One Byte) |

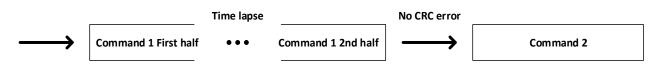

One complete command frame can be received successfully even if the bytes in the frame is not sent continuously.

CRC error could be determined by reading back the written data byte.

If host's watch dog time is disabled or time laps is within watchdog time

### 9.7.4 TRANSACTION FRAME DESCRIPTION

Command frames include the following byte types:

- 1) Frame Header Byte

- 2) Device ID Byte

- 3) Start Register Address Byte

- 4) N Data Byte(s) (N = 1~16, 32)

- 5) CRC Bytes (CRC\_L and CRC\_H)

- 6) Acknowledge Byte (ACK)

### 9.7.4.1 Frame Header Byte

The Frame Header Byte identifies the transaction as either a write/read command frame or a response frame. In addition, the Frame Header Byte indicates how many data bytes are being written/read or responded. The number of data bytes to be written/read or responded can be 1~16 or 32.

| Frame Header Type | D7       | D6   | D5   | D4:D0 |

|-------------------|----------|------|------|-------|

| CMD Frame Header  | FRM_TYPE | W/R  | BCON | CMD   |

| RSP Frame Header  | FRM_TYPE | RSVD | RSVD | RSP   |

The fields shown in the Frame Header Byte above are described in the table below.

|                  | Value (BIN)      | Description                                                                                                                   |  |  |  |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FRM_TYPE         | 0                | Response frame sent back from the IS32LT3137 device to host MCU                                                               |  |  |  |

| (Bit 7)          | 1                | Command frame sent from host MCU to the IS32LT3137 device                                                                     |  |  |  |

| W/R              | 0                | Write command frame                                                                                                           |  |  |  |

| (Bit 6)          | 1                | Read command frame                                                                                                            |  |  |  |

| BCON             | 0                | Single device write or read.                                                                                                  |  |  |  |

| (Bit 5)          | 1                | Broadcast write. The Device ID Byte must be 0xBF to broadcast to all IS32LT3137 devices. Broadcast only accepts write command |  |  |  |

|                  | Specify transmit | data length for write/read command frame:                                                                                     |  |  |  |

|                  | 00000 ~ 01111    | 1 byte ~ 16 bytes of data length                                                                                              |  |  |  |

| CMD              | 10000            | 32 bytes of data length                                                                                                       |  |  |  |

| (Bit 4:0)        | For special comr | nands (W/R bit must be set to "0"):                                                                                           |  |  |  |

|                  | 11000            | Update Command. Valid for both single device and broadcast write                                                              |  |  |  |

|                  | 11110            | Registers Reset Command. Valid for both single device and broadcast write                                                     |  |  |  |

|                  | Specify transmit | data length for response frame:                                                                                               |  |  |  |

| RSP<br>(Bit 4:0) | 00000 ~ 01111    | 1 byte ~ 16 bytes of data length                                                                                              |  |  |  |

| (2.1 1.0)        | 10000            | 32 bytes of data length                                                                                                       |  |  |  |

### 9.7.4.2 Device ID Byte

|           | D7   | D6   | D5:D0        |

|-----------|------|------|--------------|

| Device ID | p[1] | p[0] | DEV_ID [5:0] |

There are six DEV\_ID bits and two parity bits.

The parity bits for the Device ID byte are calculated with the equations below:

$p[1] = \sim (dev_id[1] \wedge dev_id[3] \wedge dev_id[4] \wedge dev_id[5])$

p[0] = dev\_id[0] ^ dev\_id[1] ^ dev\_id[2] ^ dev\_id[4]

The device ID of each IS32LT3137 device is determined by the resistors connected from three address pins of ADDR0 and ADDR1 to GND. As following mapping for the Device ID byte. For a broadcast command of UART interface, the DEV\_ID[5:0] must be 0b 111111, and the pin 30 should be left floating (Note 10), otherwise the broadcast command will be invalid.

| R <sub>AD1</sub> | R <sub>AD0</sub> | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                              |

|------------------|------------------|----|----|----|----|----|----|----|----|----------------------------------------------|

| (kΩ, N           | ote 10)          |    | 00 | 05 | 04 | 03 | DZ |    | DU | DEVICE ID (HEX)                              |

| 10k              | 10k              | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03                                           |

| 10k              | 30k              | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | D3                                           |

| 10k              | 51k              | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | A3                                           |

| 10k              | 75k              | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 1  | 73                                           |

| 30k              | 10k              | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 47                                           |

| 30k              | 30k              | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 97                                           |

| 30k              | 51k              | 1  | 1  | 1  | 0  | 0  | 1  | 1  | 1  | E7                                           |

| 30k              | 75k              | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 37                                           |

| 51k              | 10k              | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 8B                                           |

| 51k              | 30k              | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 5B                                           |

| 51k              | 51k              | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 2B                                           |

| 51k              | 75k              | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | FB                                           |

| 75k              | 10k              | 1  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | CF                                           |

| 75k              | 30k              | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1F                                           |

| 75k              | 51k              | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 6F                                           |

| 75k              | 75k              | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | BF                                           |

| -                | -                | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | BF (Note 11)<br>(for broadcast command only) |

**Note 10**: The tolerance range of resistance accuracy could be  $\pm 1\%$  or  $\pm 5\%$  for  $10k\Omega$ ,  $30k\Omega$ , and  $75k\Omega$ , but the tolerance range of resistance accuracy should be  $\pm 1\%$  for  $51k\Omega$ .

Note 11: The Device ID Byte must be 0xBF to broadcast to all IS32LT3137 devices. Broadcast only accepts write command.

Note 12: The Pin 30 should not be connected to any other pins or signals, otherwise the DEVICE ID will not be detected correctly.

Note 13: After IS32LT3137 powers on, it is suggested to wait for 3ms before sending a command, as the IS32LT3137 requires 3ms to detect its Device ID upon power-up.

### 9.7.4.3 Start Register Address Byte

The protocol allows up to 32 successive register locations from the addressed register to be written or read by a single command frame. The Start Register Address Byte is single byte which specifies the first register being written or read. The Start Register Address byte is present in only Write and Read Command transactions, not in Read Response and Special command transactions.

### 9.7.4.4 N Data Byte(s)

The Frame Header Byte specifies the number of data bytes to be included in the frame.

### 9.7.4.5 CRC Bytes (CRC\_L and CRC\_H)

The host MCU sends command to IS32LT3137 using CRC-16-IBM standard for CRC checksum calculation, which will cover the whole frame bytes, e.g., Frame Header Byte, Device ID Byte, Start Register Address Byte, N Data Bytes. Lower byte first followed by higher byte. The CRC Bytes allow detection of errors within the transaction frame. The device increments the CRC Error Count Register (59h) each time a CRC error occurs on an incoming command frame and the CRCF bit in FLT\_TYPE register (57H) will be set to "1" and the FAULTB pin will go low to report fault condition after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register).

The CRCF bit in FLT\_TYPE register (57H) is latched, which means that it cannot automatically reset to "0" when no CRC error occurs but must be cleared by the host MCU writing it back to "0". Once the CRCF bit is cleared, the FAULTB pin will go back to high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register).

The CRC bytes are also calculated by the addressed device during its Read Response. The CRC bytes are then appended to the end of the read data, lower byte first followed by higher byte. This allows the host MCU to check the read data coming from the IS32LT3137 device for any transmission errors. The following is a reference CRC checksum C code for a transmission to the IS32LT3137 devices.

```

Uint16 crc_16_ibm (Uint8 *buf, Uint8 len)

```

```

{

Uint16 crc = 0;

Uint16 l;

while (len--)

{

crc ^= *buf++;

for (l = 0; l < 8; l++){

crc = (crc >> 1) ^ ((crc & 1) ? 0xa001 : 0);

}

}

return crc;

}

```

Upon reading data from the IS32LT3137 device, the host MCU should calculate and compare the CRC to determine whether valid data was received. When IS32LT3137 sends back CRC bytes to the host MCU, the calculated CRC bytes must be bit-reversed before comparison to the received CRC bytes. The following is a reference code to perform received CRC bit reversal.

```

Uint8 reverse_byte(Uint8 byte)

```

```

{

```

```

// First, swap the nibbles

byte = (((byte & 0xF0) >> 4)| | ((byte & 0x0F) << 4));

// Then, swap bit pairs

byte = (((byte & 0xCC) >> 2) | ((byte & 0x33) << 2));

// Finally, swap adjacent bits

byte = (((byte & 0xAA) >> 1) | ((byte & 0x55) << 1));

// We should now be reversed (bit 0 <--> bit 7, bit 1 <--> bit 6, etc.)

return byte;

```

The following is a reference code for checking the read data against received CRC bytes.

```

bool is_crc_valid(Uint8 *rx_buf, Uint8 crc_start)

```

{

}

```

Uint16 crc_calc; // Calculated CRC

Uint8 crc_msb, crc_lsb; // Individual bytes of calculated CRC

// Calculate the CRC based on bytes received

crc_calc = crc_16_ibm(rx_buf, crc_start);

crc_lsb = (crc_calc & 0x00FF);

crc_msb = ((crc_calc >> 8) & 0x00FF);

// Perform the bit reversal within each byte

crc_msb = reverse_byte(crc_msb);

crc_lsb = reverse_byte(crc_lsb);

```

### 9.7.4.6 Acknowledge Byte

}

The Acknowledge Byte ("ACK") consists of a single byte (ACK=0x7F):

ACK is sent back by the addressed IS32LT3137 device only if the ACKEN bit is set in the SYSCFG register (4Ah) and only if the write is successful. A successful write yields no CRC checksum error or parity errors. Note that the acknowledge is only valid for single device write transaction of IS32LT3137.

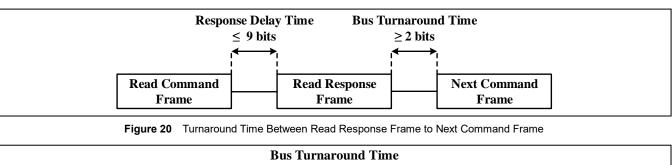

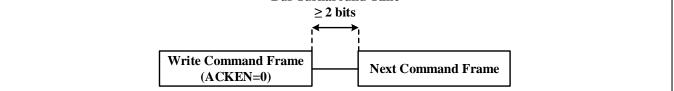

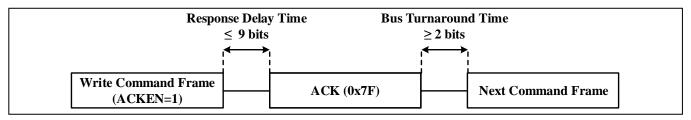

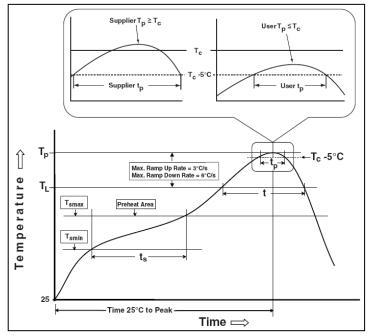

### 9.7.4.7 Turnaround Time