## **GENERAL DESCRIPTION**

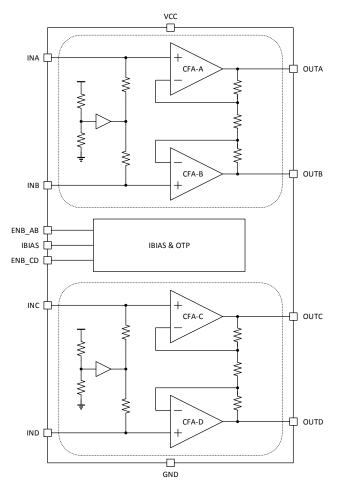

The CG1110 is a high-performance MIMO/SISO dual port differential line driver designed to work in broadband PLC system. It contains two pairs of wideband, high-voltage, current mode feedback amplifiers.

The line driver can operate on single supply from +10V to +13.2V and retains its bandwidth and linearity over the complete full-scale supply range.

The supply current can be set using a resistor on the IBIAS pin. The device has two separate disable control pins (ENB\_AB and ENB\_CD) for each differential amplifier to allow TDM operation. These logic pins are internally pulled high, so floating these inputs will put the device in shut down mode.

An internal input VCM generator maximizes the dynamic range and reduces the number of PCB components in the application circuit.

The device has built-in reliable thermal shut-down protection circuit and will be forced into shut-down mode typically when the internal junction temperature reaches +165°C.

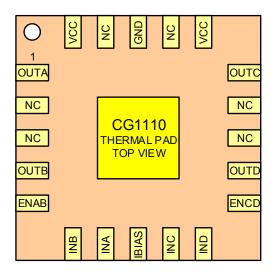

The CG1110 is available in 4mmx4mm thermally enhanced 20 pin QFN package. The device is specified for operation over the full -40°C to +85°C ambient temperature range.

### **FEATURES**

- ♦ Single +10V to +13.2V supply

- Fixed voltage gain of 25dB (A<sub>V</sub>=18 V/V)

- ◆ 100MHz -3dB closed-loop signal bandwidth

- ♦ High linearity MTPR of 50dBc

- ♦ 350mA max. output driver capability

- ♦ 16.4V<sub>pp-diff</sub> linear output drive into 34Ω

- 25mA quiescent current per port

- Control pins for enable/disable

- Internal V<sub>CM</sub> for input signal biasing

- ♦ Fast shut down / power up less than 1us

- Thermal shut-down & output short protection

- Supports 20-pin, 4mmx4mm QFN Package

- → -40°C to +85°C operating ambient temperature

#### **APPLICATIONS**

- Power Line Communications (PLC)

- Smart Grid application

- Smart Home applications (IPTV, Security Cameras, etc.)

- High Voltage and High Current Driving

# **BLOCK DIAGRAM**

Figure 1 Block diagram

# **PIN OUT (TOP VIEW)**

| PIN DESCRIPTION      |                |     |                                 |  |  |

|----------------------|----------------|-----|---------------------------------|--|--|

| PIN NUMBER           | NAME           | I/O | DESCRIPTION                     |  |  |

| 1                    | OUTA           | 0   | Amplifier-A output              |  |  |

| 2, 3, 13, 14, 17, 19 | NC             | _   | No internal connection          |  |  |

| 4                    | OUTB           | 0   | Amplifier-B output              |  |  |

| 5                    | ENB_AB         | I   | Port-AB enable/disable control  |  |  |

| 6                    | INB            | I   | Amplifier-B non-inverting input |  |  |

| 7                    | INA            | I   | Amplifier-A non-inverting input |  |  |

| 8                    | IBIAS          | 0   | Bias current adjustment pin     |  |  |

| 9                    | INC            | I   | Amplifier-C non-inverting input |  |  |

| 10                   | IND            | I   | Amplifier-D non-inverting input |  |  |

| 11                   | ENB_CD         | I   | Port-CD enable/disable control  |  |  |

| 12                   | OUTD           | 0   | Amplifier-D output              |  |  |

| 15                   | OUTC           | 0   | Amplifier-C output              |  |  |

| 16, 20               | VCC            | PW  | Power supply                    |  |  |

| 18                   | GND            | PW  | Ground                          |  |  |

| EPAD                 | THERMAL<br>PAD | I/O | Connect to the ground           |  |  |

## 1. **Operating Ranges**

## 1.1 Absolute Maximum Ratings

| Symbol                                                                        | Characteristics                | Rating         | Unit |

|-------------------------------------------------------------------------------|--------------------------------|----------------|------|

| V <sub>CC</sub>                                                               | Supply Voltage VCC to GND      | -0.3 to +13.5  | V    |

| $V_{INA}, V_{INB}, V_{INC}, V_{IND}$                                          | Voltage on input pins          | GND+3 to VCC-3 | V    |

| V <sub>ENB AB</sub> , V <sub>ENB CD</sub>                                     | Voltage on control pin         | -0.3 to +6     | V    |

| V <sub>IBIAS</sub>                                                            | Voltage on BIAS pin            | -0.3 to +4     | V    |

| I <sub>INA</sub> , I <sub>INB</sub> , I <sub>INC</sub> , I <sub>IND</sub>     | Current into any input pins    | -5 to +5       | mA   |

| I <sub>OUTA</sub> , I <sub>OUTB</sub> , I <sub>OUTC</sub> , I <sub>OUTD</sub> | DC continuous output current   | 100            | mA   |

| T <sub>Ambient</sub>                                                          | Operating ambient temperature  | -40 to 85      | °C   |

| T <sub>Junction</sub>                                                         | Operating junction temperature | 150            | °C   |

| I <sub>Latch-up</sub>                                                         | Latch up current               | 300            | mA   |

## 1.2 ESD Ratings

| ESD Rating                                    | Value | Unit |

|-----------------------------------------------|-------|------|

| Human Body Model (Tested per JESD22-A114F).   | ±2000 | V    |

| Charge Device Model (Tested per JESD22-C101E) | ±1000 | V    |

## 1.3 <u>Typical Operating Ranges</u>

| Symbol                                    | Characteristics                         | Rating       | Unit |

|-------------------------------------------|-----------------------------------------|--------------|------|

| V <sub>CC</sub>                           | Supply Voltage                          | +10 to +13.2 | V    |

| V <sub>INABD</sub> , V <sub>INCDD</sub>   | Differential input voltage at Av=18 V/V | 0 to ±1      | V    |

| V <sub>ENB AB</sub> , V <sub>ENB CD</sub> | Control pin to GND                      | 0 to +6      | V    |

| T <sub>Ambient</sub>                      | Operating temperature                   | -40 to 85    | °C   |

| T <sub>Junction</sub>                     | Junction temperature                    | -40 to 150   | °C   |

## 2. **Electrical Characteristics**

## **DC Characteristics**

$V_{CC}$  = 12V, Ta = 25°C,  $A_V$  = 18 V/V,  $R_T$  = 3.9 $\Omega$ ,  $R_{L\text{-DIFF}}$  = 34 $\Omega$ ,  $C_L$  = 50pF,  $R_{IBIAS}$  = 0 $\Omega$ , ENB\_AB = ENB\_CD = 0V, unless otherwise specified. Referred to typical test and application circuit.

| Characteristics                                              | Symbol              | Test condition                                               | Min  | Тур  | Max  | Unit   |

|--------------------------------------------------------------|---------------------|--------------------------------------------------------------|------|------|------|--------|

| Supply Characteristics                                       |                     |                                                              |      |      |      |        |

| Supply Voltage                                               | VCC                 |                                                              | 10   | 12   | 13.2 | V      |

| Quiescent Current – MIMO (Dual output port enable, 4X CFA)   | Імімо               | ENB_AB = 0V, ENB_CD = 0V                                     | -    | 46   | TBD  | mA     |

| Quiescent Current – SISO (Single output port enable, 2X CFA) | Isiso               | ENB_AB = 3.3V, ENB_CD = 0V, or<br>ENB_AB = 0V, ENB_CD = 3.3V | -    | 24   | TBD  | mA     |

| Quiescent Current - Shut Down                                | Isd                 | ENB_AB = 3.3V, ENB_CD = 3.3V                                 | -    | 1.5  | TBD  | mA     |

| Input Characteristics                                        |                     |                                                              |      | •    | •    | •      |

| Input Offset Voltage                                         | V <sub>OS_IN</sub>  | Voltage difference from INA to INB or from INC to IND        | -5   | 0    | 5    | mV     |

| Output Offset Voltage                                        | V <sub>os_out</sub> | Voltage difference from OUTA to OUTB or OUTC to OUTD         | -100 | 0    | -100 | mV     |

| Non-inverting Input Voltage Noise                            | e <sub>N</sub>      | $f_c = 1MHz^{*Note 1}$                                       | -    | 8    | -    | nV/√Hz |

| Non-inverting Input Current Noise                            | i <sub>N+</sub>     | f <sub>c</sub> = 1MHz * <sup>Note 1</sup>                    | -    | 4.5  | -    | pA/√Hz |

| Differential Input Impedance                                 | R <sub>INP</sub>    | Measured at VCC/2                                            | 10   | 12.5 | 15   | ΚΩ     |

| Logic Input High Voltage                                     | V <sub>IH</sub>     | ENB_AB, ENB_CD inputs                                        | 2.2  | -    | -    | V      |

| Logic Input Low Voltage                                      | V <sub>IL</sub>     | ENB_AB, ENB_CD inputs                                        | -    | -    | 0.8  | V      |

| Logic Input High Current                                     | I <sub>IH</sub>     | ENB_AB = ENB_CD = 3.3V                                       | -    | -3.5 | -    | μA     |

| Logic Input Low Current                                      | I <sub>IL</sub>     | ENB_AB = ENB_CD = 0V                                         | -    | 30   | -    | μA     |

| Common-mode Input Range<br>Non-Inverting Input Pins          | VCM <sub>IN</sub>   | Referenced to + VCC/2                                        | -3   | 0    | +3   | ٧      |

| Output Characteristics                                       |                     |                                                              |      |      |      |        |

| Differential Voltage Gain                                    | Av                  | (OUTA-OUTB)/(INA-INB),<br>(OUTC-OUTD)/(INC-IND)              | 17   | 18   | 19   | V/V    |

| Output Short Current                                         | I <sub>os</sub>     | $R_S$ = 1 $\Omega$ shorts to VCC or GND                      | -    | -    | 1.5  | Α      |

| Common-mode Rejection Ratio (Differential Output referred)   | CMRR <sub>DM</sub>  | f <sub>c</sub> = 1MHz, 0.1V <sub>PP</sub>                    | TBD  | 65   | -    | dB     |

| PSRR to Differential Output<br>(Output referred)             | PSRR <sub>DMO</sub> | f <sub>c</sub> = 1MHz, 0.1V <sub>PP</sub>                    | TBD  | 65   | -    | dB     |

| PSRR to Common-mode Output (Output referred)                 | PSRR <sub>CM</sub>  | f <sub>c</sub> = 1MHz, 0.1V <sub>PP</sub>                    | TBD  | 45   | -    | dB     |

| Thermal Protection                                           |                     |                                                              |      |      |      |        |

| Thermal Shut-down Temperature                                | T <sub>SD</sub>     |                                                              | -    | 165  | -    | °C     |

Note 1: Obtained from design simulation and characterization, not tested.

## **AC Characteristics**

$V_{CC}$  = 12V, Ta = 25°C, AV = 18 V/V, RT = 3.9 $\Omega$ , RL-DIFF = 34 $\Omega$ , CL = 50pF, RBIAS = 0 $\Omega$ , ENB\_AB = ENB\_CD = 0V, unless otherwise specified. Referred to typical test and application circuit.

| Characteristics             | Symbol | Test condition                             | Min | Тур  | Max | Unit |

|-----------------------------|--------|--------------------------------------------|-----|------|-----|------|

| Output AC Characteristics   |        |                                            |     |      |     |      |

| -3dB Small-signal Bandwidth | SSBW   | V <sub>IN</sub> = 0.2 V <sub>PP-DIFF</sub> | -   | 100  | -   | MHz  |

| -3dB Large-signal Bandwidth | LSBW   | V <sub>IN</sub> = 0.8 V <sub>PP-DIFF</sub> | -   | 80   | -   | MHz  |

| Slew Rate                   | SR     | V <sub>IN</sub> = 2.0 V <sub>PP-DIFF</sub> | ı   | 1600 | -   | V/µs |

| 2nd Harmonic Distortion   | HD2                                         | $f_C = 10MHz$ , $V_{IN} = 0.2 V_{PP-DIFF}$                                                                  | -   | -66 | _ | dBc |

|---------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|---|-----|

| 2nd Harmonic Distortion   | HD2                                         | $f_C = 10MHz$ , $V_{IN} = 0.8 V_{PP-DIFF}$                                                                  | -   | -60 | - | dBc |

| Ord House ania Diatortica | LIDS                                        | $f_C = 10MHz$ , $V_{IN} = 0.2 V_{PP-DIFF}$                                                                  | -   | -60 | - | dBc |

| 3rd Harmonic Distortion   | HD3 $f_C = 10MHz, V_{IN} = 0.8 V_{PP-DIFF}$ |                                                                                                             | -   | -51 | - | dBc |

|                           | MTDD                                        | Full power from 1MHz to 30MHz, 100kHz tone spacing, P <sub>LINE</sub> = 15.5dBm, PAR = 15dB                 | -50 | -   | - | dB  |

| Multi-Tone Power Ratio    | MTPR <sub>STEP</sub>                        | 30dB power back off from 30MHz to 50MHz,<br>100kHz tone spacing,<br>P <sub>LINE</sub> = 15.5dBm, PAR = 15dB | -20 | -   | - | dB  |

|                           | MTPR <sub>FLAT</sub>                        | 20dB power back off from 1MHz to 50MHz,<br>100kHz tone spacing,<br>P <sub>LINE</sub> = 15.5dBm, PAR = 15dB  | -50 | -   | - | dB  |

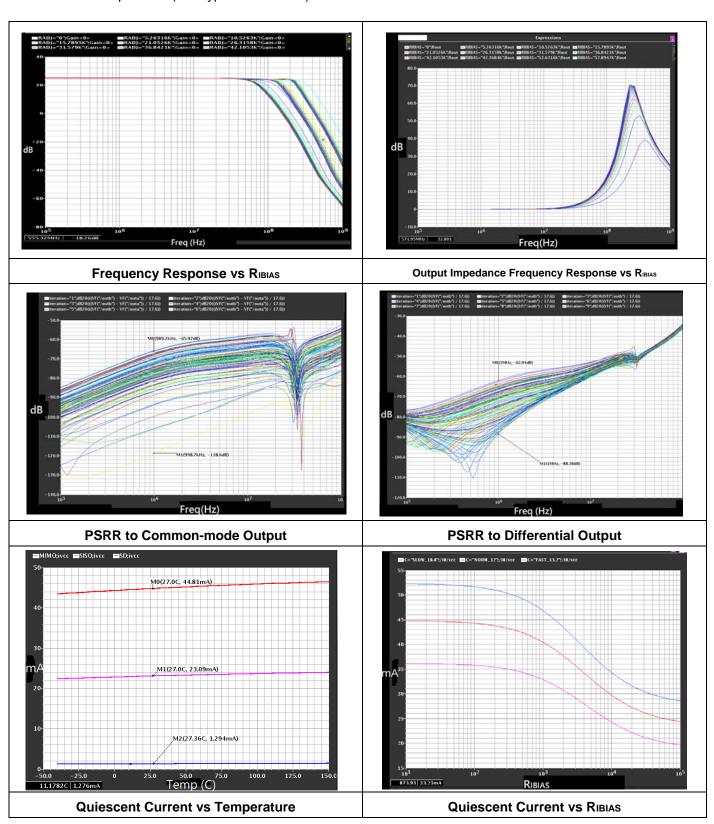

## 3. <u>Typical Performance Characteristics</u>

$V_{CC}$  = 12V, Ta = 25°C, AV =18 V/V, RT = 3.9 $\Omega$ , RL-DIFF = 34 $\Omega$ , CL = 50pF, R<sub>IBIAS</sub> = 0 $\Omega$ , ENB\_AB = ENB\_CD = 0V, unless otherwise specified. (See typical test circuit).

#### 4. Application Information

The CG1110 is a differential line driver designed for PLC line driver application. The core architecture comprises dual-pairs (four CFAs) high speed current feedback amplifiers.

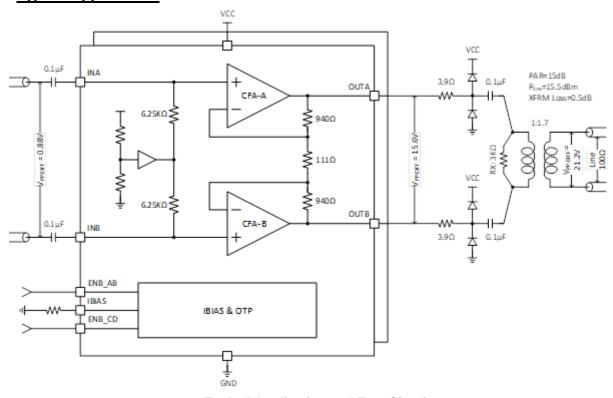

#### 4.1 Typical Applications

**Typical Application and Test Circuit**

#### 4.2 <u>Input Common Mode Voltage</u>

The analog inputs of the CG1110 are internally dc biased to VCM=VCC/2 and therefore input pins to CG1110 must be AC coupled using serial 0.1µF ceramic capacitors.

#### 4.3 Bias Current Control

The CG1110 is designed with a biasing current adjustment that lowers the quiescent operating current using an off-chip resistor ( $R_{IBIAS}$ ) that must be placed between IBIAS pin and GND. Using a resistor larger than  $0\Omega$  can reduce the quiescent current of the line driver and improve efficiency. To ensure optimized performance, it is recommended to connect the IBIAS pin to ground.

#### 4.4 Operation State Control

ENB\_AB and ENB\_CD pins are used as logic inputs to control the line driver operating states. These logic pins are designed to pull high initially, so floating these inputs will put the device in power down mode.

| ENB_AB | ENB_CD | Description                                 |

|--------|--------|---------------------------------------------|

| 0      | 0      | Port AB enable, port CD enable, MIMO mode   |

| 0      | 1      | Port AB enable, port CD disable, SISO mode  |

| 1      | 0      | Port AB disable, port CD enable, SISO mode  |

| 1      | 1      | Port AB disable, port CD disable, Shut down |

the various power modes and associated logic states. In the power-down mode, the output of the amplifier goes into a high impedance state.

#### 4.5 Thermal Shutdown

The device has thermal shutdown circuitry that protects the amplifier from damage. The thermal protection circuitry disables the device when the junction temperature reaches approximately 165°C and forces the device to cool. When the junction temperature cools to approximately 140°C, the device is automatically re-enabled.

#### 4.6 Power Dissipation and Thermal Resistance

In order to avoid performance degeneration and device damage, the junction temperature of the device is not allowed to be higher than 150°C for long time. The junction temperature given the ambient temperature is:

$$T_J = T_A + \theta_{JA} \cdot P_D$$

Where,  $T_J$  is the absolute junction temperature (°C),  $T_A$  is the ambient temperature (°C),  $\theta_{JA}$  is thermal resistance for junction to ambient (+44°C/W),  $P_D$  is the power dissipation in the line driver (W).

#### 4.7 PCB Design Guidelines

#### 4.7.1 Input Considerations:

It is recommended to keep PCB trace length as short as possible and minimize the input parasitic capacitance as much as possible to avoid any ringing or oscillation.

#### 4.7.2 Output Considerations:

The line driver has internal simple current limit protection mechanism but using  $3.9\Omega$  series output termination resistors is still recommended to limit output short current. To avoid DC current flow between the two outputs, the AC coupling capacitors are needed in series with the output.

Minimize parasitic capacitance to any ground and power plane for output pins and traces to prevent oscillation.

TVS diodes connected to VCC and GND should be used to absorb the transient energy and clamp the transient voltages of the line driver outputs. To maintain stability, the capacitance of these diodes should be less than 150pF.

#### 4.7.3 IBIAS Considerations:

The bias resistor Ribias connected to the IBIAS pin must be routed far away from the components of the signal input network in order to avoid any high frequency signal coupling into the IBIAS pin.

#### 4.7.4 Thermal pad Considerations:

The thermal pad, EPAD, must be soldered to the PCB pad and enough vias need to be used connecting to the bottom plane to dissipate heat out of the package.

#### 4.7.5 Power Supply

Use  $10\mu F$  and  $0.1\mu F$  paralleling decoupling capacitors between power supply and ground. These decoupling capacitors must be close to the power supply pins; minimizing the distance from the pins to high frequency  $0.1\mu F$  decoupling capacitors.

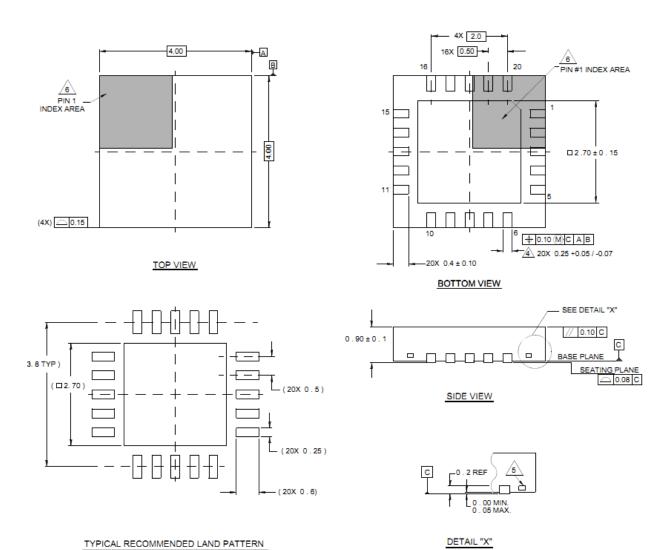

## 5. Package Outline

Note: The dimension is specified in mm.

#### 6. Ordering Information

| Order Part No.      | Package | QTY/Reel | Remark |

|---------------------|---------|----------|--------|

| IS31CG1110-QFLS2-TR | QFN-20  | 2500     |        |

Copyright © 2021 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized:

- b.) the user assumes all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

PRELIMINARY

# **MIMO/SISO** Differential Line Driver

# 7. Revisions History

| Revision | Detail Information | Date       |

|----------|--------------------|------------|

| 0A       | Initial release    | 2021.02.02 |